## **Section 15. Motor Control PWM**

### HIGHLIGHTS

This section of the manual contains the following topics:

| 15.1  | Introduction                           |       |

|-------|----------------------------------------|-------|

| 15.2  | Control Registers                      |       |

| 15.3  | PWM Time Base                          | 15-16 |

| 15.4  | PWM Duty Cycle Comparison Units        |       |

| 15.5  | Complementary PWM Output Mode          | 15-26 |

| 15.6  | Dead Time Control                      | 15-27 |

| 15.7  | Independent PWM Output Mode            |       |

|       | PWM Output Override                    |       |

| 15.9  | PWM Output and Polarity Control        | 15-34 |

|       | PWM Fault Pins                         |       |

|       | PWM Update Lockout                     |       |

| 15.12 | PWM Special Event Trigger              | 15-38 |

| 15.13 | Operation in Device Power Saving Modes | 15-38 |

|       | Special Features for Device Emulation  |       |

| 15.15 | Related Application Notes              | 15-42 |

| 15.16 | Revision History                       | 15-43 |

|       |                                        |       |

#### 15.1 Introduction

The motor control PWM (MCPWM) module simplifies the task of generating multiple, synchronized pulse width modulated outputs. In particular, the following power and motion control applications are supported:

- Three-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptable Power Supply (UPS)

The PWM module has the following features:

- Dedicated time base supports Tcy/2 PWM edge resolution

- Two output pins for each PWM generator

- · Complementary or independent operation for each output pin pair

- · Hardware dead time generators for complementary mode

- Output pin polarity programmed by device configuration bits

- Multiple output modes:

- Edge aligned mode

- Center aligned mode

- Center aligned mode with double updates

- Single event mode

- Manual override register for PWM output pins

- Duty cycle updates are configurable to be immediate or synchronized to the PWM

- Hardware fault input pins with programmable function

- Special Event Trigger for synchronizing A/D conversions

- · Each output pin associated with the PWM can be individually enabled

#### 15.1.1 MCPWM Module Variants

There are two versions of the MCPWM module depending on the dsPIC30F device that is selected. There is an 8-output module that is typically found on devices that have 64 or more pins. A 6-output MCPWM module is also available and is typically found on smaller devices that have less than 64 pins. A given dsPIC30F device may have more than one MCPWM module.

Please refer to the specific device data sheet for further details.

| Feature              | 6-Output MCPWM Module | 8-Output MCPWM Module |  |  |

|----------------------|-----------------------|-----------------------|--|--|

| I/O Pins             | 6                     | 8                     |  |  |

| PWM Generators       | 3                     | 4                     |  |  |

| Fault Input Pins     | 1                     | 2                     |  |  |

| Dead Time Generators | 1                     | 2                     |  |  |

Table 15-1:

Feature Summary: 6-Output MCPWM vs. 8-Output MCPWM

The 6-output MCPWM module is useful for single or 3-phase power application, while the 8 MCPWM can support 4-phase motor applications. Table 15-1 provides a feature summary for 6- and 8-output MCPWM modules. Both modules can support multiple single phase loads. The 8-output MCPWM also provides increased flexibility in an application because it supports two fault pins and two programmable dead times. These features are discussed in greater detail in subsequent sections.

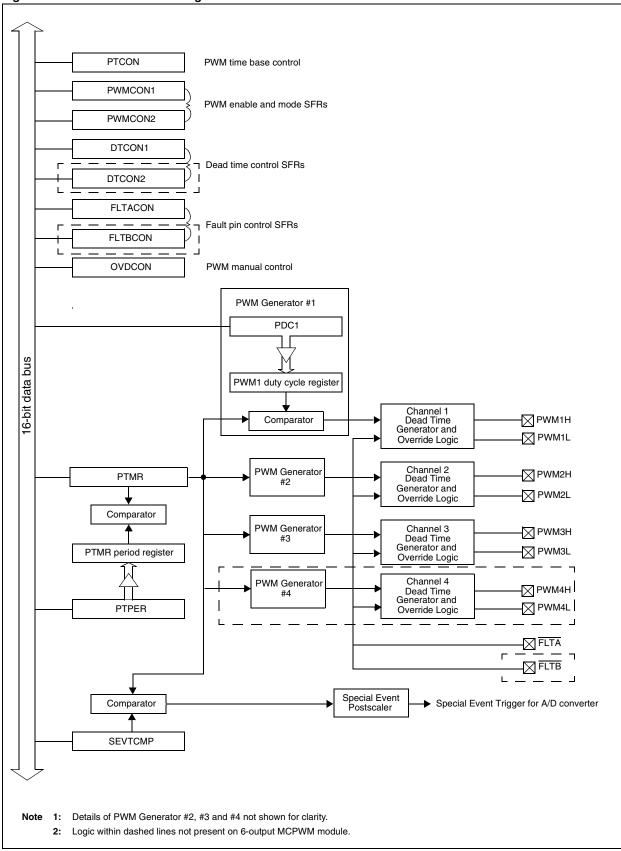

A simplified block diagram of the MCPWM module is shown in Figure 15-1.

Figure 15-1: MCPWM Block Diagram

#### 15.2 Control Registers

The following registers control the operation of the MCPWM module:

- PTCON: PWM Time Base Control register

- PTMR: PWM Time Base register

- PTPER: PWM Time Base Period register

- SEVTCMP: PWM Special Event Compare register

- PWMCON1: PWM Control register #1

- PWMCON2: PWM Control register #2

- DTCON1: Dead Time Control register #1

- DTCON2: Dead Time Control register #2

- FLTACON: Fault A Control register

- FLTBCON: Fault B Control register

- PDC1: PWM Duty Cycle register #1

- PDC2: PWM Duty Cycle register #2

- PDC3: PWM Duty Cycle register #3

- PDC4: PWM Duty Cycle register #4

In addition, there are three device configuration bits associated with the MCPWM module to set up the initial Reset states and polarity of the I/O pins. These configuration bits are located in the FBORPOR device configuration register. Please refer to **Section 24.** "**Device Configuration**" for further details.

| Jpper B | yte:                                         |                         |             |                |                |             |       |

|---------|----------------------------------------------|-------------------------|-------------|----------------|----------------|-------------|-------|

| R/W-0   | U-0 R/W                                      | /-0 U-0                 | U-0         | U-0 U-         | •0 U·          | -0          |       |

| PTEN    | — PTS                                        | DL —                    | _           |                |                | _           |       |

| it 15   |                                              |                         |             |                |                | bit 8       |       |

|         |                                              |                         |             |                |                |             |       |

|         | Lower Byte:                                  |                         |             |                |                |             |       |

|         | R/W-0                                        | R/W-0 R/W-0             | R/W-0       | R/W-0          | R/W-0          | R/W-0       | R/W-0 |

|         |                                              | PTOPS<3:0>              |             | PTCKP          | S<1:0>         | PTMOD<      |       |

|         | bit 7                                        |                         |             |                |                |             | bit   |

| it 15   | PTEN: PWM Time Bas                           | a Timor Enabla bit      |             |                |                |             |       |

| 1115    | 1 = PWM time base is                         |                         |             |                |                |             |       |

|         | 0 = PWM time base is                         | -                       |             |                |                |             |       |

| it 14   | Unimplemented: Rea                           | <b>d as</b> '0'         |             |                |                |             |       |

| it 13   | PTSIDL: PWM Time E                           | ase Stop in Idle Mode   | bit         |                |                |             |       |

|         | 1 = PWM time base ha                         |                         |             |                |                |             |       |

|         | 0 = PWM time base ru                         |                         |             |                |                |             |       |

| it 12-8 | Unimplemented: Rea                           |                         |             |                |                |             |       |

| oit 7-4 | PTOPS<3:0>: PWM T<br>1111 = 1:16 Postscale   |                         | scale Selec | t bits         |                |             |       |

|         | •                                            | ;                       |             |                |                |             |       |

|         | •                                            |                         |             |                |                |             |       |

|         | 0001 = 1:2 Postscale                         |                         |             |                |                |             |       |

|         | 0000 = 1:1 Postscale                         |                         |             |                |                |             |       |

| oit 3-2 | PTCKPS<1:0>: PWM                             | Time Base Input Cloc    | k Prescale  | Select bits    |                |             |       |

|         | 11 = PWM time base i                         |                         |             |                |                |             |       |

|         | 10 = PWM time base i<br>01 = PWM time base i |                         |             |                |                |             |       |

|         | 00 = PWM time base i                         |                         |             |                |                |             |       |

| oit 1-0 | PTMOD<1:0>: PWM ]                            |                         |             | ,              |                |             |       |

|         | 11 = PWM time base                           |                         |             | mode with inte | errupts for do | uble PWM up | dates |

|         | 10 = PWM time base of                        |                         |             | counting mode  | e              |             |       |

|         | 01 = PWM time base 0<br>00 = PWM time base 0 |                         |             |                |                |             |       |

|         | $00 = \mathbf{r}$ volvi time base (          | operates in a nee fulli | ing mode    |                |                |             |       |

|         | Legend:                                      |                         |             |                |                |             |       |

|         | · ·                                          |                         |             |                |                | (0)         |       |

|         | R = Readable bit                             | W = Writable bit        | U           | = Unimplemer   | ited bit, read | l as '0'    |       |

### dsPIC30F Family Reference Manual

| Register 15- | 2: F | PTMR: PW | M Time Ba | se Registe | r         |            |       |        |      |       |

|--------------|------|----------|-----------|------------|-----------|------------|-------|--------|------|-------|

| Upper Byte   | :    |          |           |            |           |            |       |        |      |       |

| R-0          | R/\  | N-0 F    | R/W-0     | R/W-0      | R/W-0     | R/W-0      | R/W-0 | R/W-0  |      |       |

| PTDIR        |      |          |           | PTI        | MR <14:8> |            |       |        |      |       |

| bit 15       |      |          |           |            |           |            |       | bit    | 8    |       |

|              |      |          |           |            |           |            |       |        |      |       |

|              |      | Lower By | vte:      |            |           |            |       |        |      |       |

|              |      | R/W-0    | R/W-0     | ) R/W-0    | 0 R/W     | /-0 R/\    | N-0 R | /W-0 R | /W-0 | R/W-0 |

|              |      |          |           |            | F         | PTMR <7:0> | >     |        |      |       |

|              |      | bit 7    |           |            |           |            |       |        |      | bit ( |

bit 15 PTDIR: PWM Time Base Count Direction Status bit (Read Only) 1 = PWM time base is counting down 0 = PWM time base is counting up

bit 14-0 PTMR <14:0>: PWM Timebase Register Count Value

| Legend:                                                          |                  |                      |                    |  |  |

|------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

| Register 15-3: | PTPER: PWM Time Base Period Register |

|----------------|--------------------------------------|

|                |                                      |

| Upper Byte | e:           |       |       |       |       |       |       |  |  |  |  |

|------------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| U-0        | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

| _          | PTPER <14:8> |       |       |       |       |       |       |  |  |  |  |

| bit 15     |              |       |       |       |       |       | bit 8 |  |  |  |  |

| Lower Byte | e:          |       |       |       |       |       |       |  |  |  |  |

|------------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| R/W-0      | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|            | PTPER <7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7      |             |       |       |       |       |       | bit 0 |  |  |  |  |

#### bit 15 Unimplemented: Read as '0'

bit 14-0 PTPER<14:0>: PWM Time Base Period Value bits

| Legend:           |                  |                                                 |                    |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

| Register 15-4 | : SEVTCN | IP: Special I | Event Comp | are Registe | r         |         |         |          |

|---------------|----------|---------------|------------|-------------|-----------|---------|---------|----------|

| Upper Byte:   |          |               |            |             |           |         |         |          |

| R/W-0         | R/W-0    | R/W-0         | R/W-0      | R/W-0       | R/W-0     | R/W-0   | R/W-0   |          |

| SEVTDIR       |          |               | SEV1       | CMP <14:8   | >         |         |         |          |

| bit 15        |          |               |            |             |           |         | bit 8   |          |

|               |          |               |            |             |           |         |         |          |

|               | Lower    | Byte:         |            |             |           |         |         |          |

|               | R/W-     | -0 R/W-       | 0 R/W-     | 0 R/W-      | 0 R/V     | V-0 R/V | V-0 R/W | -0 R/W-0 |

|               |          |               |            | SEV         | TCMP <7:0 | )>      |         |          |

|               | bit 7    |               |            |             |           |         |         | bit 0    |

bit 15 SEVTDIR: Special Event Trigger Time Base Direction bit<sup>(1)</sup>

1 = A special event trigger will occur when the PWM time base is counting downwards.

0 = A special event trigger will occur when the PWM time base is counting upwards.

- bit 14-0 SEVTCMP <14:0>: Special Event Compare Value bit<sup>(2)</sup>

- **Note 1:** SEVTDIR is compared with PTDIR (PTMR<15>) to generate the special event trigger.

- **2:** SEVTCMP<14:0> is compared with PTMR<14:0> to generate the special event trigger.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### Register 15-5: PWMCON1: PWM Control Register 1

| Upper Byte | e:  |     |     |       |       |       |       |

|------------|-----|-----|-----|-------|-------|-------|-------|

| U-0        | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|            | —   | —   | —   | PMOD4 | PMOD3 | PMOD2 | PMOD1 |

| bit 15     |     |     |     |       |       |       | bit 8 |

| Lower Byte | <b>:</b> |       |       |       |       |       |       |

|------------|----------|-------|-------|-------|-------|-------|-------|

| R/W-1      | R/W-1    | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| PEN4H      | PEN3H    | PEN2H | PEN1H | PEN4L | PEN3L | PEN2L | PEN1L |

| bit 7      |          |       |       |       |       |       | bit 0 |

#### bit 15-12 Unimplemented: Read as '0'

- bit 11-8 PMOD4: PMOD1: PWM I/O Pair Mode bits

1 = PWM I/O pin pair is in the independent output mode

0 = PWM I/O pin pair is in the complementary output mode

bit 7-4 PEN4H-PEN1H: PWMxH I/O Enable bits<sup>(1)</sup>

- bit 7-4 PEN4H-PENTH: PWMXH I/O Enable bits<sup>(1)</sup> 1 = PWMxH pin is enabled for PWM output 0 = PWMxH pin disabled. I/O pin becomes general purpose I/O bit 3-0 PEN4L-PEN1L: PWMxL I/O Enable bits<sup>(1)</sup>

- 1 = PWMxL pin is enabled for PWM output

- 0 = PWMxL pin disabled. I/O pin becomes general purpose I/O

- **Note 1:** Reset condition of the PENxH and PENxL bits depend on the value of the PWM/PIN device configuration bit in the FBORPOR Device Configuration Register.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented,   | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# dsPIC30F Family Reference Manual

| Register  | 15-6: PWMC                      | ON2: PWM C      | ontrol Regis    | ter 2          |               |              |        |       |

|-----------|---------------------------------|-----------------|-----------------|----------------|---------------|--------------|--------|-------|

| Upper B   | yte:                            |                 |                 |                |               |              |        |       |

| U-0       | U-0                             | U-0             | U-0             | R/W-0          | R/W-0         | R/W-0        | R/W-0  |       |

|           | —                               |                 |                 |                | SEVOP         | S<3:0>       |        |       |

| bit 15    |                                 |                 |                 |                |               |              | bit 8  |       |

|           |                                 |                 |                 |                |               |              |        |       |

|           | Lower                           | Byte:           |                 |                |               |              |        |       |

|           | U-0                             | U-0             | U-0             | U-0            | U-0           | R/W-0        | R/W-0  | R/W-0 |

|           |                                 | —               | —               | —              | —             | IUE          | OSYNC  | UDIS  |

|           | bit 7                           |                 |                 |                |               |              |        | bit 0 |

|           |                                 |                 |                 |                |               |              |        |       |

| bit 15-12 | Unimplement                     | ed: Read as '   | 0'              |                |               |              |        |       |

| bit 11-8  | SEVOPS<3:0                      |                 | ial Event Trigg | ger Output Po  | ostscale Sele | ect bits     |        |       |

|           | 1111 = <b>1</b> : <b>1</b> 6 F  | ostscale        |                 |                |               |              |        |       |

|           | •                               |                 |                 |                |               |              |        |       |

|           | •                               |                 |                 |                |               |              |        |       |

|           | 0001 = 1:2 Pc<br>0000 = 1:1 Pc  |                 |                 |                |               |              |        |       |

| bit 7-2   |                                 |                 | o'              |                |               |              |        |       |

|           | •                               |                 |                 |                |               |              |        |       |

| bit 2     | IUE: Immediat<br>1 = Updates to |                 |                 | re immediate   |               |              |        |       |

|           | 0 = Updates to                  |                 | 0               |                |               | VM time base |        |       |

| bit 1     | OSYNC: Outp                     |                 | 0               | -              |               |              |        |       |

|           |                                 |                 |                 |                | chronized to  | the PWM time | e base |       |

|           | 0 = Output ov                   | errides via the | OVDCON reg      | gister occur o | n next TCY b  | oundary      |        |       |

| bit 0     | UDIS: PWM L                     | Ipdate Disable  | e bit           |                |               |              |        |       |

|           | 1 = Updates fi                  |                 |                 | •              |               |              |        |       |

|           | 0 = Updates fi                  | om duty cycle   | e and period b  | uffer register | s are enable  | d            |        |       |

|           |                                 |                 |                 |                |               |              |        |       |

| Note 1: IUE bit is not implemented on the dsPIC30F6010 device |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| Register 15-7 | 7: DTCON1 | I: Dead Time | Control Reg | ister 1 |       |          |       |       |       |

|---------------|-----------|--------------|-------------|---------|-------|----------|-------|-------|-------|

| Upper Byte:   |           |              |             |         |       |          |       |       |       |

| R/W-0         | R/W-0     | R/W-0        | R/W-0       | R/W-0   | R/W-0 | R/W-0    | R/W-0 | C     |       |

| DTBPS         | S<1:0>    |              |             | DTB<5   | :0>   |          |       |       |       |

| bit 15        |           |              |             |         |       |          | b     | it 8  |       |

|               |           |              |             |         |       |          |       |       |       |

|               | Lower B   | yte:         |             |         |       |          |       |       |       |

|               | R/W-0     | R/W-0        | R/W-0       | R/W-    | 0 R/\ | N-0 R    | /W-0  | R/W-0 | R/W-0 |

|               | DT        | APS<1:0>     |             |         |       | DTA<5:0> |       |       |       |

|               | bit 7     |              |             |         |       |          |       |       | bit 0 |

bit 15-14 **DTBPS<1:0>:** Dead Time Unit B Prescale Select bits

- 11 = Clock period for Dead Time Unit B is 8 TCY

- 10 =Clock period for Dead Time Unit B is 4 TCY

- 01 = Clock period for Dead Time Unit B is 2 Tcy

- 00 =Clock period for Dead Time Unit B is TCY

- bit 13-8 DTB<5:0>: Unsigned 6-bit Dead Time Value bits for Dead Time Unit B

- bit 7-6 DTAPS<1:0>: Dead Time Unit A Prescale Select bits

- 11 = Clock period for Dead Time Unit A is 8 TCY

- 10 = Clock period for Dead Time Unit A is 4 TCY

- Ol = Clock period for Dead Time Unit A is 2 Tcy

- ${\tt 0\,0}$  = Clock period for Dead Time Unit A is TCY

- bit 5-0 DTA<5:0>: Unsigned 6-bit Dead Time Value bits for Dead Time Unit A

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented,   | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

15 Motor Control PWM

## dsPIC30F Family Reference Manual

| Register 15-8: DTCON2: Dead Time Control Register 2 |                                                                                                         |                             |             |                 |             |          |            |            |            |         |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|-------------|-----------------|-------------|----------|------------|------------|------------|---------|

| Upper By                                            | yte:                                                                                                    |                             |             |                 |             |          |            |            |            |         |

| U-0                                                 |                                                                                                         | U-0                         | U-0         | U-0             | U-0         | U-0      | U          | -0         | U-0        |         |

|                                                     |                                                                                                         | _                           | _           | —               | _           |          | -          | -          | _          |         |

| bit 15                                              |                                                                                                         |                             |             |                 |             |          |            |            | bit 8      |         |

|                                                     |                                                                                                         |                             |             |                 |             |          |            |            |            |         |

|                                                     |                                                                                                         | Lower Byt                   |             |                 |             |          |            |            |            |         |

|                                                     |                                                                                                         | R/W-0                       | R/W-0       | R/W-0           | R/W-        | 0        | R/W-0      | R/W-C      | ) R/W-     | 0 R/W-0 |

|                                                     |                                                                                                         | DTS4A                       | DTS4I       | DTS3A           | DTS         | 31       | DTS2A      | DTS2       | I DTS1     | A DTS1I |

|                                                     |                                                                                                         | bit 7                       |             |                 |             |          |            |            |            | bit 0   |

|                                                     |                                                                                                         |                             |             |                 |             |          |            |            |            |         |

| bit 15-8                                            | Unimplemented: Read as '0'                                                                              |                             |             |                 |             |          |            |            |            |         |

| bit 7                                               |                                                                                                         |                             |             | it for PWM4 S   | ignal Going | Active   |            |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

| h.H. O                                              |                                                                                                         | ead time pro                |             |                 |             |          | _          |            |            |         |

| bit 6                                               | <b>DTS4I:</b> Dead Time Select bit for PWM4 Signal Going Inactive<br>1 = Dead time provided from Unit B |                             |             |                 |             |          |            |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

| bit 5                                               | DTS3A: Dead Time Select bit for PWM3 Signal Going Active                                                |                             |             |                 |             |          |            |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 | 0 0         |          |            |            |            |         |

|                                                     | $0 = \mathbf{D}$                                                                                        | ead time pro                | ovided from | Unit A          |             |          |            |            |            |         |

| bit 4                                               |                                                                                                         |                             |             | for PWM3 Sig    | gnal Going  | Inactive | e          |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

| L:1 0                                               |                                                                                                         | ead time pro                |             |                 | :           | A        |            |            |            |         |

| bit 3                                               |                                                                                                         | A: Dead Tin<br>ead time pro |             | it for PWM2 S   | ignal Going | Active   |            |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

| bit 2                                               |                                                                                                         | •                           |             | for PWM2 Sig    | anal Going  | Inactive | e          |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 | 5           |          |            |            |            |         |

|                                                     | 0 = D                                                                                                   | ead time pro                | ovided from | Unit A          |             |          |            |            |            |         |

| bit 1                                               |                                                                                                         |                             |             | it for PWM1 S   | ignal Going | Active   |            |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

| 1.11.0                                              |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

| bit 0                                               |                                                                                                         | ead time pro                |             | t for PWM1 Sig  | gnal Going  | Inactive | e          |            |            |         |

|                                                     |                                                                                                         | ead time pro                |             |                 |             |          |            |            |            |         |

|                                                     |                                                                                                         |                             |             |                 |             |          |            |            |            |         |

|                                                     | Leger                                                                                                   | nd:                         |             |                 |             |          |            |            |            |         |

|                                                     | R = R                                                                                                   | eadable bit                 |             | W = Writable    | bit         | U =      | Unimpler   | nented, re | ead as '0' |         |

|                                                     | I                                                                                                       | alue at POF                 | 2           | '1' = Bit is se | +           | ·0'      | Bit is cle | arod       | x = Bit is | unknown |

| Register | 15-9: FLTACON: Fau                                                                                                                                                                                                              | IIt A Control Regi    | ster   |          |             |             |         |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|----------|-------------|-------------|---------|--|--|--|

| Upper B  | Syte:                                                                                                                                                                                                                           |                       |        |          |             |             |         |  |  |  |

| R/W-0    | R/W-0 R/W                                                                                                                                                                                                                       | -0 R/W-0              | R/W-0  | R/W-0    | R/W-0       | R/W-0       |         |  |  |  |

| FAOV4    | H FAOV4L FAOV                                                                                                                                                                                                                   | /3H FAOV3L            | FAOV2H | FAOV2L   | FAOV1H      | FAOV1L      |         |  |  |  |

| bit 15   |                                                                                                                                                                                                                                 |                       |        |          |             | bit 8       |         |  |  |  |

|          |                                                                                                                                                                                                                                 |                       |        |          |             |             |         |  |  |  |

|          | Lower Byte:                                                                                                                                                                                                                     |                       |        |          |             |             |         |  |  |  |

|          | R/W-0                                                                                                                                                                                                                           | <u>U-0</u> U-0        | ) U-   |          | V-0 R/V     |             |         |  |  |  |

|          | FLTAM                                                                                                                                                                                                                           |                       |        | - FA     | EN4 FAE     | N3 FAEN     | 2 FAEN1 |  |  |  |

|          | bit 7                                                                                                                                                                                                                           |                       |        |          |             |             | bit 0   |  |  |  |

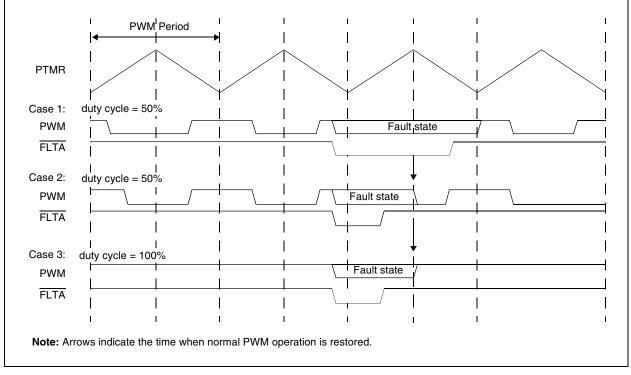

| bit 15-8 | bit 15-8 FAOV4H-FAOV1L: Fault Input A PWM Override Value bits<br>1 = The PWM output pin is driven ACTIVE on an external fault input event<br>0 = The PWM output pin is driven INACTIVE on an external fault input event         |                       |        |          |             |             |         |  |  |  |

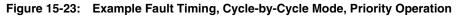

| bit 7    | <ul> <li>FLTAM: Fault A Mode bit</li> <li>1 = The Fault A input pin functions in the cycle-by-cycle mode</li> <li>0 = The Fault A input pin latches all control pins to the programmed states in FLTACON&lt;15:8&gt;</li> </ul> |                       |        |          |             |             |         |  |  |  |

| bit 6-4  | Unimplemented: Rea                                                                                                                                                                                                              | d as '0'              |        |          |             |             |         |  |  |  |

| bit 3    | <b>FAEN4:</b> Fault Input A B<br>1 = PWM4H/PWM4L p<br>0 = PWM4H/PWM4L p                                                                                                                                                         | in pair is controlled |        |          |             |             |         |  |  |  |

| bit 2    | <b>FAEN3:</b> Fault Input A E<br>1 = PWM3H/PWM3L p<br>0 = PWM3H/PWM3L p                                                                                                                                                         | in pair is controlled |        |          |             |             |         |  |  |  |

| bit 1    | <ul> <li>FAEN2: Fault Input A Enable bit</li> <li>1 = PWM2H/PWM2L pin pair is controlled by Fault Input A</li> <li>0 = PWM2H/PWM2L pin pair is not controlled by Fault Input A</li> </ul>                                       |                       |        |          |             |             |         |  |  |  |

| bit 0    | <b>FAEN1:</b> Fault Input A E<br>1 = PWM1H/PWM1L p<br>0 = PWM1H/PWM1L p                                                                                                                                                         | in pair is controlled |        |          |             |             |         |  |  |  |

|          | Legend:                                                                                                                                                                                                                         |                       |        |          |             |             |         |  |  |  |

|          | R = Readable bit                                                                                                                                                                                                                | W = Writab            | e bit  | U = Unir | nplemented, | read as '0' |         |  |  |  |

|          |                                                                                                                                                                                                                                 |                       |        |          |             |             |         |  |  |  |

| Upper By | /te:                                                                                                                                                                            |                                  |                                            |                |                     |          |             |           |       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------|----------------|---------------------|----------|-------------|-----------|-------|

| R/W-0    | R/W-0                                                                                                                                                                           | R/W-0                            | R/W-0                                      | R/W-0          | R/W-0               | R/V      | V-0 R       | /W-0      |       |

| FBOV4H   | FBOV4L                                                                                                                                                                          | FBOV3H                           | FBOV3L                                     | FBOV2H         | FBOV2               | _ FBO    | V1H FB      | OV1L      |       |

| bit 15   |                                                                                                                                                                                 |                                  |                                            |                |                     |          |             | bit 8     |       |

|          |                                                                                                                                                                                 | <u> </u>                         |                                            |                |                     |          |             |           |       |

|          | Lower                                                                                                                                                                           | -                                |                                            |                |                     |          | -           | -         | -     |

|          | R/W-                                                                                                                                                                            |                                  | 0 U-                                       | <u>0 U</u>     | -                   | R/W-0    | R/W-0       | R/W-0     | R/W-0 |

|          | FLTB                                                                                                                                                                            | SM                               |                                            |                | -   F               | BEN4     | FBEN3       | FBEN2     | FBEN1 |

|          | bit 7                                                                                                                                                                           |                                  |                                            |                |                     |          |             |           | bit 0 |

| bit 7    | FLTBM: Fault I<br>1 = The Fault E<br>0 = The Fault E                                                                                                                            | 3 input pin fu<br>3 input pin la | tches all cont                             |                |                     | med stat | tes in FLTE | 3CON<15:8 | >     |

| bit 6-4  | Unimplemente                                                                                                                                                                    |                                  |                                            |                |                     |          |             |           |       |

| bit 3    | <b>FAEN4:</b> Fault Input B Enable bit <sup>(1)</sup><br>1 = PWM4H/PWM4L pin pair is controlled by Fault Input B<br>0 = PWM4H/PWM4L pin pair is not controlled by Fault Input B |                                  |                                            |                |                     |          |             |           |       |

|          | 0 = PWM4H/P                                                                                                                                                                     | WM4L pin pa                      | air is not cont                            | rolled by Fau  |                     |          |             |           |       |

| bit 2    | 0 = PWM4H/P<br><b>FAEN3:</b> Fault I<br>1 = PWM3H/P'<br>0 = PWM3H/P'                                                                                                            | nput B Enat<br>WM3L pin pa       | ole bit <sup>(1)</sup><br>air is controlle | ed by Fault In | It Input B<br>put B |          |             |           |       |

#### Register 15-10: FLTBCON: Fault B Control Register

FAEN1: Fault Input B Enable bit<sup>(1)</sup>

1 = PWM1H/PWM1L pin pair is controlled by Fault Input B 0 = PWM1H/PWM1L pin pair is not controlled by Fault Input B **Note 1:** Fault pin A has priority over Fault pin B, if enabled.

W = Writable bit

'1' = Bit is set

bit 0

Legend:

R = Readable bit

-n = Value at POR

x = Bit is unknown

U = Unimplemented, read as '0'

'0' = Bit is cleared

bit 0

|            |        |         |        | - <b>3</b> |        |          |         |        |     |

|------------|--------|---------|--------|------------|--------|----------|---------|--------|-----|

| Upper Byte | ):     |         |        |            |        |          |         |        |     |

| R/W-1      | R/W-1  | R/W-1   | R/W-1  | R/W-       | I R/V  | V-1 R/W  | /-1 R/V | N-1    |     |

| POVD4H     | POVD4L | POVD3H  | POVD3L | POVD2      | 2H POV | D2L POVI | D1H POV | /D1L   |     |

| bit 15     |        |         |        |            |        |          |         | bit 8  |     |

|            |        |         |        |            |        |          |         |        |     |

|            | Lower  | Byte:   |        |            |        |          |         |        |     |

|            | R/W-   | 0 R/W-  | 0 R/   | N-0        | R/W-0  | R/W-0    | R/W-0   | R/W-0  | R/V |

|            | POUT   | 4H POUT | 4L POL | ЈТЗН Р     | OUT3L  | POUT2H   | POUT2L  | POUT1H | POU |

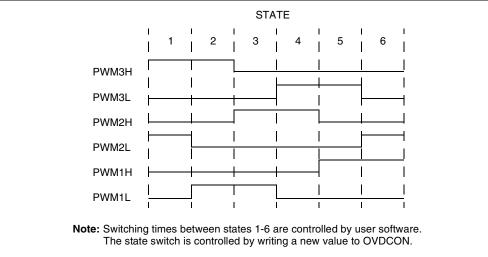

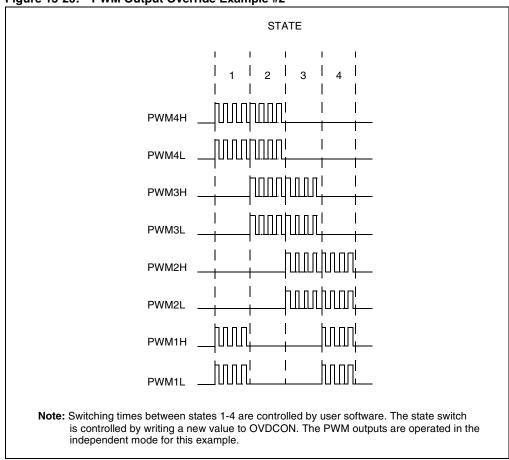

#### Register 15-11: OVDCON: Override Control Register

#### bit 15-8 POVD4H-POVD1L: PWM Output Override bits

bit 7

1 = Output on PWMxx I/O pin is controlled by the PWM generator

0 = Output on PWMxx I/O pin is controlled by the value in the corresponding POUTxx bit

#### bit 7-0 POUT4H-POUT1L: PWM Manual Output bits

1 = PWMxx I/O pin is driven ACTIVE when the corresponding POVDxx bit is cleared

0 = PWMxx I/O pin is driven INACTIVE when the corresponding POVDxx bit is cleared

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented,   | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### Register 15-12: PDC1: PWM Duty Cycle Register 1

| Upper Byte | ):    |       |              |                |       |       |       |

|------------|-------|-------|--------------|----------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0        | R/W-0          | R/W-0 | R/W-0 | R/W-0 |

|            |       | PW    | M Duty Cycle | e #1 bits 15-8 | 3     |       |       |

| bit 15     |       |       |              |                |       |       | bit 8 |

| Lower Byte | e:    |       |            |                |       |       |       |

|------------|-------|-------|------------|----------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0      | R/W-0          | R/W-0 | R/W-0 | R/W-0 |

|            |       | P     | WM Duty Cy | /cle #1 bits 7 | -0    |       |       |

| bit 7      |       |       |            |                |       |       | bit 0 |

#### bit 15-0 PDC1<15:0>: PWM Duty Cycle #1 Value bits

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### Register 15-13: PDC2: PWM Duty Cycle Register 2

| Upper Byte | :     |       |              |                |       |       |       |

|------------|-------|-------|--------------|----------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0        | R/W-0          | R/W-0 | R/W-0 | R/W-0 |

|            |       | PW    | M Duty Cycle | e #2 bits 15-8 | 3     |       |       |

| bit 15     |       |       |              |                |       |       | bit 8 |

| Lower Byte | e:    |       |            |               |       |       |       |

|------------|-------|-------|------------|---------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0      | R/W-0         | R/W-0 | R/W-0 | R/W-0 |

|            |       | Р     | WM Duty Cy | cle #2 bits 7 | -0    |       |       |

| bit 7      |       |       |            |               |       |       | bit 0 |

#### bit 15-0 PDC2<15:0>: PWM Duty Cycle #2 Value bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### Register 15-14: PDC3: PWM Duty Cycle Register 3

| Upper Byte | :     |       |              |                |       |       |       |

|------------|-------|-------|--------------|----------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0        | R/W-0          | R/W-0 | R/W-0 | R/W-0 |

|            |       | PW    | M Duty Cycle | e #3 bits 15-8 | 3     |       |       |

| bit 15     |       |       |              |                |       |       | bit 8 |

| Lower Byte | ə:    |       |            |               |       |       |       |

|------------|-------|-------|------------|---------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0      | R/W-0         | R/W-0 | R/W-0 | R/W-0 |

|            |       | Р     | WM Duty Cy | cle #3 bits 7 | -0    |       |       |

| bit 7      |       |       |            |               |       |       | bit 0 |

#### bit 15-0 PDC3<15:0>: PWM Duty Cycle #3 Value bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### Register 15-15: PDC4: PWM Duty Cycle Register 4

| Upper Byte                  | :     |       |       |       |       |       |       |

|-----------------------------|-------|-------|-------|-------|-------|-------|-------|

| R/W-0                       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| PWM Duty Cycle #4 bits 15-8 |       |       |       |       |       |       |       |

| bit 15                      |       |       |       |       |       |       | bit 8 |

| Lower Byte | ə:    |       |            |                |       |       |       |

|------------|-------|-------|------------|----------------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0      | R/W-0          | R/W-0 | R/W-0 | R/W-0 |

|            |       | Р     | WM Duty Cy | /cle #4 bits 7 | -0    |       |       |

| bit 7      |       |       |            |                |       |       | bit 0 |

#### bit 15-0 PDC4<15:0>: PWM Duty Cycle #4 Value bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### Register 15-16: FBORPOR: BOR AND POR Device Configuration Register

| Upper Byte | e:  |     |     |     |     |     |        |

|------------|-----|-----|-----|-----|-----|-----|--------|

| U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

| —          |     | —   | —   | _   | _   | _   | —      |

| bit 23     |     |     |     |     |     |     | bit 16 |

| Middle Byt | e:  |     |     |     |        |      |       |

|------------|-----|-----|-----|-----|--------|------|-------|

| U-0        | U-0 | U-0 | U-0 | U-0 | R/P    | R/P  | R/P   |

|            | —   |     | —   | _   | PWMPIN | HPOL | LPOL  |

| bit 15     |     |     |     |     |        |      | bit 8 |

| Lower Byte | e:  |     |        |     |     |      |        |

|------------|-----|-----|--------|-----|-----|------|--------|

| R/P        | U-0 | R/P | R/P    | U-0 | U-0 | R/P  | R/P    |

| BOREN      | _   | BOR | /<1:0> | _   | _   | FPWF | T<1:0> |

| bit 7      |     |     |        |     |     |      | bit 0  |

#### bit 10 **PWMPIN: MPWM Drivers Initialization bit** 1 = Pin state at reset controlled by I/O Port (PWMCON1<7:0> = $0 \times 00$ ) 0 = Pin state at reset controlled by module (PWMCON1<7:0> = 0xFF)bit 9 HPOL: MCPWM High Side Drivers (PWMxH) Polarity bit 1 = Output signal on PWMxH pins has active high polarity 0 = Output signal on PWMxH pins has active low polarity bit 8 LPOL: MCPWM Low Side Drivers (PWMxL) Polarity bit 1 = Output signal on PWMxL pins has active high polarity 0 = Output signal on PWMxL pins has active low polarity See Section 24. "Device Configuration" for information about other configuration bits on this Note: register. Legend: R = Readable bit W = Writable bit U = Unimplemented, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

P = Programmable configuration bit

© 2005 Microchip Technology Inc.

15

Motor Control PWM

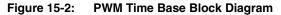

#### 15.3 PWM Time Base

The PWM time base is provided by a 15-bit timer with a prescaler and postscaler (see Figure 15-2). The 15 bits of the time base are accessible via the PTMR register. PTMR<15> is a read-only status bit, PTDIR, that indicates the present count direction of the PWM time base. If the PTDIR status bit is cleared, PTMR is counting upwards. If PTDIR is set, PTMR is counting downwards.

The time base is enabled/disabled by setting/clearing the PTEN bit (PTCON<15>). PTMR is not cleared when the PTEN bit is cleared in software.

The PWM time base can be configured for four different modes of operation:

- 1. Free Running mode

- 2. Single Event mode

- 3. Continuous Up/Down Count mode

- 4. Continuous Up/Down Count mode with interrupts for double-updates.

These four modes are selected by the PTMOD<1:0> control bits (PTCON<1:0>).

**Note:** The mode of the PWM time base determines the type of PWM signal that is generated by the module. (See Section 15.4.2, Section 15.4.3 and Section 15.4.4 for more details.)

#### 15.3.1 Free Running Mode

In the Free Running mode, the time base will count upwards until the value in the PTPER register is matched. The PTMR register is reset on the following input clock edge and the time base will continue counting upwards as long as the PTEN bit remains set.

#### 15.3.2 Single-Event Mode

In the Single Event Counting mode, the PWM time base will begin counting upwards when the PTEN bit is set. When the PTMR value matches the PTPER register, the PTMR register will be reset on the following input clock edge and the PTEN bit will be cleared by the hardware to halt the time base.

#### 15.3.3 Up/Down Counting Modes

For the Continuous Up/Down Counting modes, the PWM time base will count upwards until the value in the PTPER register is matched. The timer will begin counting downwards on the following input clock edge and continue counting down until it reaches '0'. The PTDIR bit PTMR<15> is read-only and indicates the counting direction. The PTDIR bit is set when the timer counts downwards.

#### 15.3.4 PWM Time Base Prescaler

The input clock to PTMR, (TcY) has prescaler options of 1:1, 1:4, 1:16 or 1:64 selected by control bits PTCKPS<1:0> (PTCON<3:2>). The prescaler counter is cleared when any of the following occurs:

- A write to the PTMR register

- A write to the PTCON register

- Any device reset

The PTMR register is not cleared when PTCON is written.

#### 15.3.5 PWM Time Base Postscaler

The match output of PTMR can optionally be post-scaled through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate an interrupt. The postscaler is useful when the PWM duty cycle does not need to be updated every PWM cycle.

The postscaler counter is cleared when any of the following occurs:

- A write to the PTMR register

- A write to the PTCON register

- Any device reset

The PTMR register is not cleared when PTCON is written.

#### 15.3.6 PWM Time Base Interrupts

The interrupt signals generated by the PWM time base depend on the mode selection bits, PTMOD<1:0> (PTCON<1:0>), and the time base postscaler bits, PTOPS<3:0> (PTCON<7:4>).

#### • Free Running Mode

When the PWM time base is in the Free Running mode (PTMOD<1:0> = 0.0), an interrupt is generated when the PTMR register is reset to '0', due to a match with the PTPER register. The postscaler selection bits may be used in this mode of the timer to reduce the frequency of the interrupt events.

#### Single Event Mode

When the PWM time base is in the Single Event mode (PTMOD<1:0> = 01), an interrupt is generated when the PTMR register is reset to '0' due to a match with the PTPER register. The PTEN bit (PTCON<15>) is also cleared at this time to inhibit further PTMR increments. The postscaler selection bits have no effect in this mode of the timer.

#### Up/Down Counting Mode

In the Up/Down Counting mode (PTMOD<1:0> = 10), an interrupt event is generated each time the value of the PTMR register becomes zero and the PWM time base begins to count upwards. The postscaler selection bits may be used in this mode of the timer to reduce the frequency of the interrupt events.

#### Up/Down Counting Mode with Double Updates

In the Double Update mode (PTMOD<1:0> = 11), an interrupt event is generated each time the PTMR register is equal to zero and each time a period match occurs. The postscaler selection bits have no effect in this mode of the timer.

The Double Update mode allows the control loop bandwidth to be doubled because the PWM duty cycles can be updated twice per period. Every rising and falling edge of the PWM signal can be controlled using the double update mode.

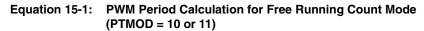

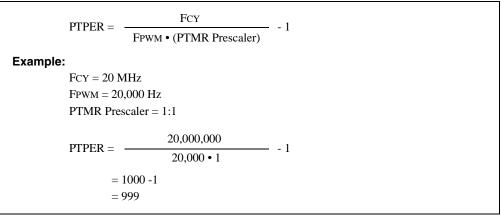

#### 15.3.7 PWM Period

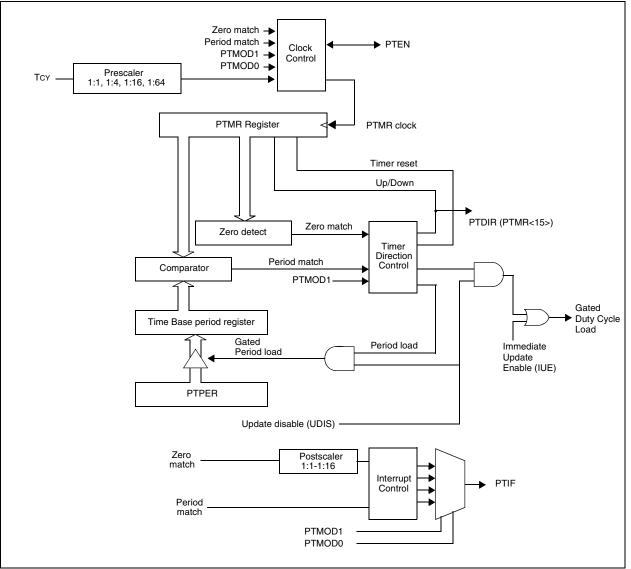

The PTPER register sets the counting period for PTMR. The user must write a 15-bit value to PTPER<14:0>. When the value in PTMR<14:0> matches the value in PTPER<14:0>, the time base will either reset to '0' or reverse the count direction on the next clock input edge. The action taken depends on the operating mode of the time base.

The time base period is double buffered to allow on-the-fly period changes of the PWM signal without glitches. The PTPER register serves as a buffer register to the actual time base period register, which is not accessible by the user. The PTPER register contents are loaded into the actual time base period register at the following times:

- Free Running and Single Event modes: when the PTMR register is reset to zero after a match with the PTPER register.

- Up/Down Counting modes: When the PTMR register is zero.

The value held in the PTPER register is automatically loaded into the time base period register when the PWM time base is disabled (PTEN = 0).

Figure 15-3 and Figure 15-4 indicate the times when the contents of the PTPER register are loaded into the time base period register.

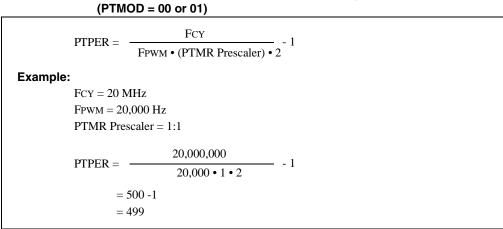

The PWM period can be determined from the following formula:

### Equation 15-2: PWM Period Calculation in Up/Down Counting Modes

#### 15.4 PWM Duty Cycle Comparison Units

The MCPWM module has four PWM generators. There are four 16-bit special function registers used to specify duty cycle values for the PWM generators:

- PDC1

- PDC2

- PDC3

- PDC4

In subsequent discussions, PDCx refers to any of the four PWM duty cycle registers.

#### 15.4.1 PWM Duty Cycle Resolution

The maximum resolution (in bits) for a given device oscillator and PWM frequency can be determined from the following formula:

#### Equation 15-3: PWM Resolution

| Resol | $ution = \frac{\log\left(\frac{2TPWM}{TCY}\right)}{\log(2)}$ |  |

|-------|--------------------------------------------------------------|--|

|       | $\log(2)$                                                    |  |

The PWM resolutions and frequencies are shown in Table 15-2 for a selection of execution speeds and PTPER values. The PWM frequencies in Table 15-2 are for edge-aligned (Free Running PTMR) PWM mode. For center aligned modes (Up/Down PTMR mode), the PWM frequencies will be 1/2 the values as indicated in Table 15-3.

| Table 15-2: | Example PWM Frequencies and Resolutions, 1:1 Prescaler, Edge Aligned |

|-------------|----------------------------------------------------------------------|

|             | PWM                                                                  |

| TCY (FCY)       | PTPER Value | PDCx Value for<br>100% | PWM<br>Resolution | PWM Frequency |

|-----------------|-------------|------------------------|-------------------|---------------|

| 33 ns (30 MHz)  | 0x7FFF      | 0xFFFF                 | 16 bits           | 915 Hz        |

| 33 ns (30 MHz)  | 0x3FF       | 0x7FF                  | 11 bits           | 29.3 kHz      |

| 50 ns (20 MHz)  | 0x7FFF      | 0xFFFF                 | 16 bits           | 610 Hz        |

| 50 ns (20 MHz)  | 0x1FF       | 0x3FF                  | 10 bits           | 39.1 kHz      |

| 100 ns (10 MHz) | 0x7FFF      | 0xFFFF                 | 16 bits           | 305 Hz        |

| . ,             | 0xFF        | 0x1FF                  | 9 bits            | 39.1 kHz      |

| 100 ns (10 MHz) | 0x7FF       | 0xFFFF                 |                   |               |

| 200 ns (5 MHz)  | -           | -                      | 16 bits           | 153 Hz        |

| 200 ns (5 MHz)  | 0x7F        | 0xFF                   | 8 bits            | 39.1 kHz      |

| , v             |             |                        |                   |               |

|-----------------|-------------|------------------------|-------------------|---------------|

| TCY (FCY)       | PTPER Value | PDCx Value for<br>100% | PWM<br>Resolution | PWM Frequency |

| 33 ns (30 MHz)  | 0x7FFF      | 0xFFFF                 | 16 bits           | 458 Hz        |

| 33 ns (30 MHz)  | 0x3FFF      | 0x7FFF                 | 15 bits           | 916 Hz        |

| 50 ns (20 MHz)  | 0x7FFF      | 0xFFFF                 | 16 bits           | 305 Hz        |

| 50 ns (20 MHz)  | 0x1FFF      | 0x3FFF                 | 14 bits           | 1.22 kHz      |

| 100 ns (10 MHz) | 0x7FFF      | 0xFFFF                 | 16 bits           | 153 Hz        |

| 100 ns (10 MHz) | 0xFFF       | 0x1FFF                 | 13 bits           | 1.22 kHz      |

| 200 ns (5 MHz)  | 0x7FFF      | 0xFFFF                 | 16 bits           | 76.3 Hz       |

| 200 ns (5 MHz)  | 0x7FF       | 0xFFF                  | 12 bits           | 1.22 kHz      |

Table 15-3:

Example PWM Frequencies and Resolutions, 1:1 Prescaler, Center

Aligned PWM

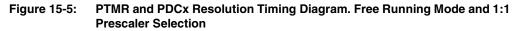

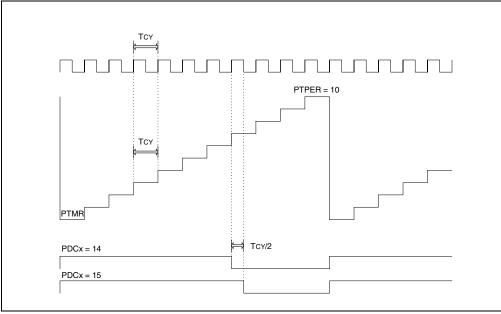

The MCPWM module has the ability to produce PWM signal edges with Tcy/2 resolution. PTMR increments every Tcy with a 1:1 prescaler. To achieve Tcy/2 edge resolution, PDCx<15:1> is compared to PTMR<14:0> to determine a duty cycle match. PDCx<0> determines whether the PWM signal edge will occur at the Tcy or the Tcy/2 boundary. When a 1:4, 1:16 or a 1:64 prescaler is used with the PWM time base, PDCx<0> is compared to the MSbit of the prescaler counter clock to determine when the PWM edge should occur.

PTMR and PDCx resolutions are depicted in Figure 15-5. It is shown that PTMR resolution is Tcy and PDCx resolution is Tcy/2 for 1:1 prescaler selection.

#### Figure 15-6: Duty Cycle Comparison Logic

#### 15.4.2 Edge Aligned PWM

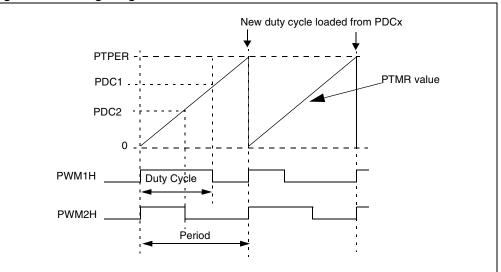

Edge aligned PWM signals are produced by the module when the PWM time base is operating in the Free Running mode. The output signal for a given PWM channel has a period specified by the value loaded in PTPER and a duty cycle specified by the appropriate PDCx register (see Figure 15-7). Assuming a non-zero duty cycle and no immediate updates are enabled (IUE = 0), the outputs of all enabled PWM generators will be driven active at the beginning of the PWM period (PTMR = 0). Each PWM output will be driven inactive when the value of PTMR matches the duty cycle value of the PWM generator.

If the value in the PDCx register is zero, then the output on the corresponding PWM pin will be inactive for the entire PWM period. In addition, the output on the PWM pin will be active for the entire PWM period if the value in the PDCx register is greater than the value held in the PTPER register.

If immediate updates are enabled (IUE = 1), the new duty cycle value will be loaded at the time the new value is written to any active PDC register.

Figure 15-7: Edge-Aligned PWM

#### 15.4.3 Single Event PWM Operation

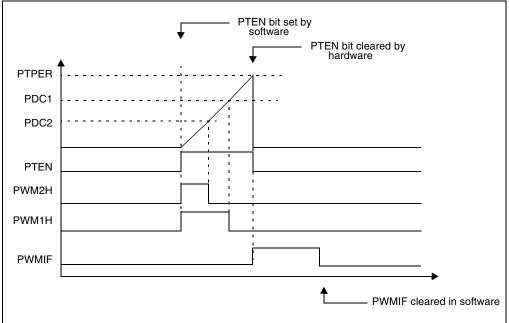

The PWM module will produce single pulse outputs when the PWM time base is configured for the single event mode (PTMOD<1:0> = 01). This mode of operation is useful for driving certain types of electronically commutated motors. In particular, this mode is useful for high-speed SR motor operation. Only edge-aligned outputs may be produced in the Single Event mode.

In Single Event mode, the PWM I/O pin(s) are driven to the active state when the PTEN bit is set. When a match with a duty cycle register occurs, the PWM I/O pin is driven to the inactive state. When a match with the PTPER register occurs, the PTMR register is cleared, all active PWM I/O pins are driven to the inactive state, the PTEN bit is cleared, and an interrupt is generated. Operation of the PWM module will stop until the PTEN is set again in software.

Figure 15-8: Single Event PWM Operation

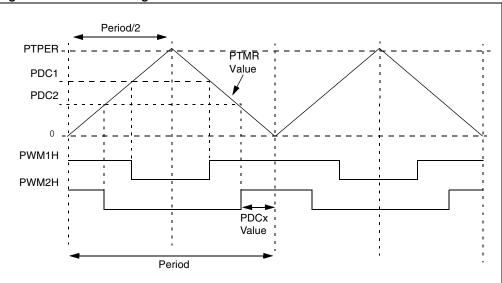

#### 15.4.4 Center Aligned PWM

Center aligned PWM signals are produced by the module when the PWM time base is configured in one of the two Up/Down Counting modes (PTMOD<1:0> = 1x).

The PWM compare output is driven to the active state when the value of the Duty Cycle register matches the value of PTMR and the PWM time base is counting downwards (PTDIR = 1). The PWM compare output will be driven to the inactive state when the PWM time base is counting upwards (PTDIR = 0) and the value in the PTMR register matches the duty cycle value.

If the value in a particular Duty Cycle register is zero, then the output on the corresponding PWM pin will be inactive for the entire PWM period. In addition, the output on the PWM pin will be active for the entire PWM period if the value in the Duty Cycle register is greater than the value held in the PTPER register.

#### 15.4.5 Duty Cycle Register Buffering

The four PWM duty cycle registers, PDC1-PDC4, are buffered to allow glitchless updates of the PWM outputs. For each generator, there is the PDCx register (buffer register) that is accessible by the user and the non-memory mapped Duty Cycle register that holds the actual compare value. The PWM duty cycle is updated with the value in the PDCx register at specific times in the PWM period to avoid glitches in the PWM output signal.

When the PWM time base is operating in the Free Running or Single Event modes (PTMOD<1:0> = 0x), the PWM duty cycle is updated whenever a match with the PTPER register occurs and PTMR is reset to '0'.

**Note:** Any write to the PDCx registers will immediately update the duty cycle when the PWM time base is disabled (PTEN = 0). This allows a duty cycle change to take effect before PWM signal generation is enabled.

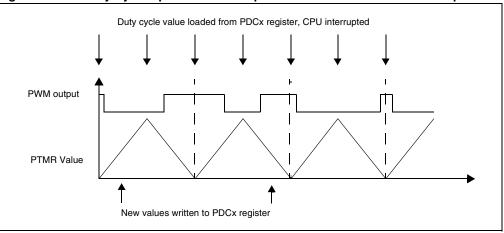

When the PWM time base is operating in the Up/Down Counting mode (PTMOD<1:0> = 10), duty cycles are updated when the value of the PTMR register is zero and the PWM time base begins to count upwards. Figure 15-10 indicates the times when the duty cycle updates occur for this mode of the PWM time base.

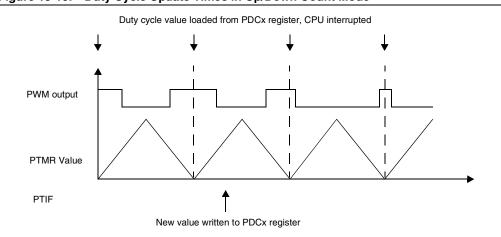

When the PWM time base is in the Up/Down Counting mode with double updates (PTMOD<1:0> = 11), duty cycles are updated when the value of the PTMR register is zero and when the value of the PTMR register matches the value in the PTPER register. Figure 15-11 indicates the times when the duty cycle updates occur for this mode of the PWM time base.

#### Figure 15-10: Duty Cycle Update Times in Up/Down Count Mode

Figure 15-11: Duty Cycle Update Times in Up/Down Count Mode with Double Updates

#### 15.4.6 PWM Duty Cycle Immediate Updates

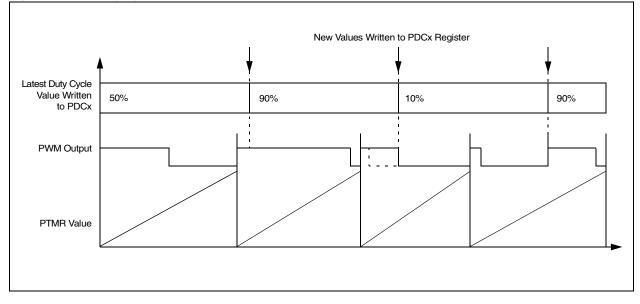

When the Immediate Update Enable bit is set (IUE = 1), any write to the duty cycle registers will update the new duty cycle value immediately. This feature gives the option to the user to allow immediate updates of the active PWM duty cycle registers instead of waiting for the end of the current time base period. System stability is improved in closed loop servo applications by reducing the delay between system observation and the issuance of system corrective commands when immediate updates are enabled (IUE = 1).

If the PWM output is active at the time the new duty cycle is written and the new duty cycle is less than the current time base value, the PWM pulse width will be shortened. If the PWM output is active at the time the new duty cycle is written and the new duty cycle is greater than the current time base value, the PWM pulse width will be lengthened. If the PWM output is inactive at the time the new duty cycle is written and the new duty cycle is greater than the current time base value, the PWM pulse width will be lengthened. If the PWM output is inactive at the time the new duty cycle is written and the new duty cycle is greater than the current time base value, the PWM output will become active immediately and will remain active for the new written duty cycle value.

Figure 15-12 indicates the times when the duty cycle updates occur when immediate updates are enabled (IUE = 1).

**Note:** The IUE bit is not implemented on the dsPIC30F6010 device.

#### 15.5 Complementary PWM Output Mode

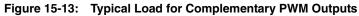

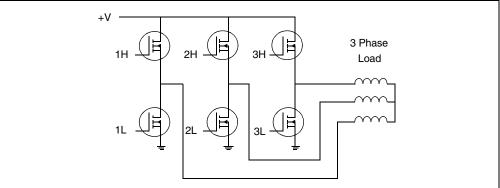

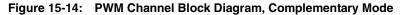

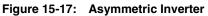

The Complementary Output mode is used to drive inverter loads similar to the one shown in Figure 15-13. This inverter topology is typical for ACIM and BLDC applications. In the Complementary Output mode, a pair of PWM outputs cannot be active simultaneously. Each PWM channel and output pin pair is internally configured as shown in Figure 15-14. A dead time may be optionally inserted during device switching where both outputs are inactive for a short period (Refer to **Section 15.6 "Dead Time Control"**).

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in PWMCON1. The PWM I/O pins are set to complementary mode by default upon a device reset.

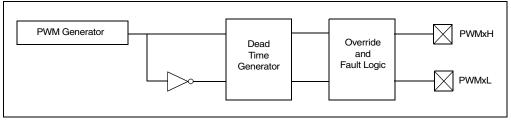

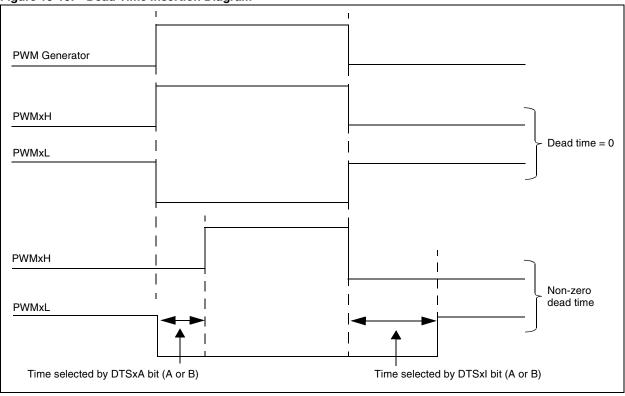

#### 15.6 Dead Time Control

Dead time generation is automatically enabled when any of the PWM I/O pin pairs are operating in the Complementary Output mode. Because the power output devices cannot switch instantaneously, some amount of time must be provided between the turn-off event of one PWM output in a complementary pair and the turn-on event of the other transistor.

The 6-output PWM module has one programmable dead time. The 8-output PWM module allows two different dead times to be programmed. These two dead times may be used in one of two methods described below to increase user flexibility:

- The PWM output signals can be optimized for different turn-off times in the high-side and low-side transistors. The first dead time is inserted between the turn-off event of the lower transistor of the complementary pair and the turn-on event of the upper transistor. The second dead time is inserted between the turn-off event of the upper transistor and the turn-on event of the lower transistor.

- The two dead times can be assigned to individual PWM I/O pin pairs. This operating mode allows the PWM module to drive different transistor/load combinations with each complementary PWM I/O pin pair.

#### 15.6.1 Dead Time Generators

Each complementary output pair for the PWM module has a 6-bit down counter that is used to produce the dead time insertion. As shown in Figure 15-15, each dead time unit has a rising and falling edge detector connected to the duty cycle comparison output.