# dsPIC30F2011/ 2012/3012/3013

## dsPIC30F2011/2012/3012/3013 Rev. A1 Silicon Errata

### dsPIC30F2011/2012/3012/3013 (Rev. A1) Silicon Errata

The dsPIC30F2011/2012/3012/3013 (Rev. A1) samples you have received were found to conform to the specifications and functionality described in the following documents:

- DS70030 dsPIC30F Programmer's Reference Manual

- DS70139 dsPIC30F2011/2012/3012/3013 Data Sheet

- DS70046 dsPIC30F Family Reference Manual

The exceptions to the specifications in the documents listed above are described in this section. The specific devices for which these exceptions are described are listed below:

- dsPIC30F2011

- dsPIC30F2012

- dsPIC30F3012

- dsPIC30F3013

These devices may be identified by the following message that appears in the MPLAB<sup>®</sup> ICD 2 Output Window under MPLAB IDE, when a "reset-and-connect" operation is performed within MPLAB IDE:

Setting Vdd source to target

Target Device dsPIC30F3013 found, revision = Rev 1001

...Reading ICD Product ID

Running ICD Self Test

...Passed

MPLAB ICD 2 Ready

The errata described in this section will be fixed in future revisions of dsPIC30F2011, dsPIC30F2012, dsPIC30F3012 and dsPIC30F3013 devices.

### Silicon Errata Summary

The following list summarizes the errata described in further detail throughout the remainder of this document:

1. Malfunction of EMUC2 pin on dsPIC30F2011/ 2012/3012/3013

On the dsPIC30F2011/2012/3012/3013, the EMUC2 pin is susceptible to negative voltage spikes and requires additional protection.

### 2. Data EEPROM

The Most Significant bit of every 4th byte in data EEPROM may be corrupted.

3. Decimal Adjust Instruction

The Decimal Adjust instruction, DAW.b, may improperly clear the Carry bit, C (SR<0>).

4. PSV Operations Using SR

In certain instructions, fetching one of the operands from program memory using Program Space Visibility (PSV) will corrupt specific bits in the Status Register, SR.

5. Early Termination of Nested DO Loops

When using two DO loops in a nested fashion, terminating the inner-level DO loop by setting the EDT (CORCON<11>) bit will produce unexpected results.

6. x4 PLL Operation

The x4 PLL mode of operation may not function correctly for certain input frequencies.

7. Sequential Interrupts

Sequential interrupts after modifying the CPU IPL, interrupt IPL, interrupt enable or interrupt flag may cause an Address Error trap.

8. Using OSC2/RC15 pin for Digital I/O

For this revision of silicon, if the pin RC15 is required for digital input/output, the FPR<4:0> bits in the FOSC Configuration register may not be set up for FRC w/PLL 4x/8x/16x modes.

The following sections will describe the errata and work around to these errata, where they may apply.

# 1. Module: Malfunction of EMUC2 pin on dsPIC30F2011/2012/3012/3013

On the dsPIC30F2011/2012/3012/3013 devices, the EMUC2 pin is susceptible to negative voltage spikes and requires additional protection.

### Work around

The work around depends on the usage of the EMUC2 pin.

- If the EMUC2 pin is not used, terminate pin to ground through a 100 ohm resistor.

- If the EMUC2 pin is used for emulation, connect pin to the ICD 2 EMUC signal through a 100 ohm resistor.

- If the EMUC2 pin is used for I/O, add low-pass RC filter on the pin, with C = 1 nF and R = 100 ohm with the capacitor junction on the pin.

### 2. Module: Data EEPROM

The Most Significant bit of every fourth byte in data EEPROM may be corrupted on any write operation. This write corruption may occur while using either PRO MATE<sup>®</sup>, MPLAB ICD 2 or Run-Time Self-Programming (RTSP).

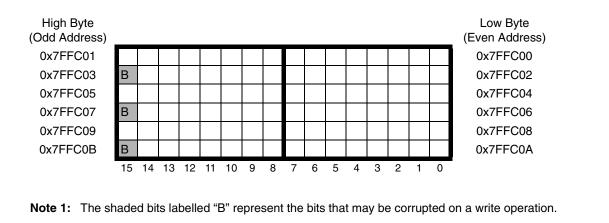

Figure 1 shows the first twelve bytes in data EEPROM and indicates the affected bits.

2: The memory map shown here depicts only the first twelve bytes of device EEPROM.

### Work around

### Work Around 1:

Use program Flash memory instead of data EEPROM to store constant data.

### Work Around 2:

Use less than 16 bits in each word in the available data EEPROM, excluding the Most Significant bit.

### Work Around 3:

Avoid using every fourth byte. Example 1 shows how the ASM30 assembler can be used to allocate data in the EEPROM under this constraint.

### EXAMPLE 1:

| .includ | le '  | p30f3013 | 3.inc"  |       |

|---------|-------|----------|---------|-------|

| .sectio | on .  | .eedata, | "r"     |       |

| .align  | 4     |          |         |       |

| .hword  | 0xF34 | 45       |         |       |

| .byte   | 0x23  |          |         |       |

| .byte   | 0xFF  |          | ;Unused | byte  |

| .hword  | 0x123 | 34       |         |       |

| .byte   | 0x23  |          |         |       |

| .byte   | 0xFF  |          | ;Unused | byte" |

### 3. Module: CPU - DAW.b Instruction

The Decimal Adjust instruction, DAW.b, may improperly clear the Carry bit, C (SR<0>), when executed.

### Work around

Check the state of the Carry bit prior to executing the DAW.b instruction. If the Carry bit is set, set the Carry bit again after executing the DAW.b instruction. Example 2 shows how the application should process the Carry bit during a BCD addition operation.

### EXAMPLE 2:

| .include "p30f3013.inc" |            |                    |

|-------------------------|------------|--------------------|

|                         |            |                    |

| MOV.b                   | #0x80, w0  | ;First BCD number  |

| MOV.b                   | #0x80, w1  | ;Second BCD number |

| ADD.b                   | w0, w1, w2 | ;Perform addition  |

| BRA                     | NC, LO     | ;If C set go to LO |

| DAW.b                   | w2         | ;If not,do DAW and |

| BSET.b                  | SR, #C     | ;set the carry bit |

| BRA                     | L1         | ;and exit          |

| L0:DAW.b                | w2         |                    |

| L1:                     |            |                    |

### 4. Module: PSV Operations Using SR

When one of the operands of instructions shown in Table 1 is fetched from program memory using Program Space Visibility (PSV), the Status Register, SR and/or the results may be corrupted. These instructions are identified in Table 1. Example 3 demonstrates one scenario where this occurs.

### TABLE 1:

| Instruction <sup>(2)</sup>  | Examples of Inco      | orrect Operation | Data Corruption IN                         |

|-----------------------------|-----------------------|------------------|--------------------------------------------|

| ADDC                        | ADDC W0, [W1++], W2   | ;See Note 1      | SR<1:0> bits <sup>(3)</sup> , Result in W2 |

| SUBB                        | SUBB.b W0, [++W1], W3 | ;See Note 1      | SR<1:0> bits <sup>(3)</sup> , Result in W3 |

| СРВ                         | CPB W0, [W1++], W4    | ;See Note 1      | SR<1:0> bits <sup>(3)</sup>                |

| RLC                         | RLC [W1], W4          | ;See Note 1      | SR<1:0> bits <sup>(3)</sup> , Result in W4 |

| RRC                         | RRC [W1], W2          | ;See Note 1      | SR<1:0> bits <sup>(3)</sup> , Result in W2 |

| ADD (Accumulator-<br>based) | ADD [W1++], A         | ;See Note 1      | SR<1:0> bits <sup>(4)</sup>                |

| LAC                         | LAC [W1], A           | ;See Note 1      | SR<15:10> bits <sup>(4)</sup>              |

**Note 1:** The errata only affects these instructions when a PSV access is performed to fetch one of the source operands in the instruction. A PSV access is performed when the Effective Address of the source operand is greater than 0x8000 and the PSV (CORCON<2>) bit is set to '1'. In the examples shown, the data access from program memory is made via the W1 register.

- 2: Refer to the Programmer's Reference Manual for details on the dsPIC30F instruction set.

- 3: SR<1:0> bits represent Sticky Zero and Carry status bits respectively.

- 4: SR<15:10> bits represent Accumulator Overflow and Saturation status bits

### EXAMPLE 3:

| .include "p30fxxxx.inc" |                |                       |  |

|-------------------------|----------------|-----------------------|--|

|                         |                |                       |  |

| MOV.B                   | #0x00, W0      | ;Load PSVPAG register |  |

| MOV.B                   | WREG, PSVPAG   |                       |  |

| BSET                    | CORCON, #PSV   | ;Enable PSV           |  |

|                         |                |                       |  |

| MOV                     | #0x8200, W1    | ;Set up W1 for        |  |

|                         |                | ;indirect PSV access  |  |

|                         |                | ;from 0x000200        |  |

| ADD                     | W3, [W1++], W5 | ;This instruction     |  |

|                         |                | ;works ok             |  |

| ADDC                    | W4, [W1++], W6 | ;Carry flag and       |  |

|                         |                | ;W6 gets              |  |

|                         |                | ;corrupted here!      |  |

### Work around

## Work Around 1: For Assembly Language Source Code

To work around the erratum in the MPLAB<sup>®</sup> ASM30 assembler, the application may perform a PSV access to move the source operand from program memory to RAM or a W register prior to performing the operations listed in Table 1. The work around for Example 3 is demonstrated in Example 4.

### EXAMPLE 4:

| .include "p30fxxxx.inc"                   |                                                          |  |

|-------------------------------------------|----------------------------------------------------------|--|

| <br>MOV.B #0x00, w0<br>MOV.B WREG, PSVPAG | ;Load PSVPAG register                                    |  |

| BSET CORCON, #PSV                         | ;Enable PSV                                              |  |

| <br>MOV #0x8200, W1                       | ;Set up W1 for<br>;indirect PSV access<br>;from 0x000200 |  |

| ADD W3, [W1++], W5                        | ,                                                        |  |

| MOM [M1] MO                               | ;works ok                                                |  |

| MOV [W1++], W2                            | ;Load W2 with data<br>;from program memory               |  |

| ADDC W4, W2, W6                           | ;Carry flag and W4<br>;results are ok!                   |  |

### Work Around 2: For C Language Source Code

For applications using C language, MPLAB C30 versions 1.20.04 or higher provide the following command-line switch that implements a work around for the erratum.

#### -merrata=psv

Refer to the "readme.txt" file in the MPLAB C30 v1.20.04 toolsuite for further details.

# 5. Module: Early Termination of Nested DO Loops

When using two DO loops in a nested fashion, terminating the inner-level DO loop by setting the EDT (CORCON<11>) bit will produce unexpected results. Specifically, the device may continue executing code within the outer DO loop forever. This erratum does not affect the operation of the MPLAB C30 compiler.

### Work around

The application should save the DCOUNT SFR prior to entering the inner DO loop and restore it upon exiting the inner DO loop. This work around is shown in Example 5.

### EXAMPLE 5:

|        | .include "p30fxxxx.inc"                                                                                            |                                        |

|--------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|        | DO #CNT1, LOOP0                                                                                                    | ;Outer loop start                      |

|        | PUSH DCOUNT<br>DO #CNT2, LOOP1<br><br>BTSS Flag, #0                                                                | ;Save DCOUNT<br>;Inner loop<br>;starts |

|        | BSET CORCON, #EDT                                                                                                  | ;Terminate inner<br>;DO-loop early     |

| LOOP1: | MOV W1, W5<br>POP DCOUNT                                                                                           | ;Inner loop ends<br>;Restore DCOUNT    |

| LOOP0: | <br>Mov w5, w8                                                                                                     | ;Outer loop ends                       |

| Note:  | For details on the functionality of<br>EDT bit, see section 2.9.2.4<br>in the dsPIC30F Family Reference<br>Manual. |                                        |

### 6. Module: PLL

When the x4 PLL mode of operation is selected, the specified input frequency range of 4-10 MHz is not fully supported.

When device VDD is 2.5-3.0V, the x4 PLL input frequency must be in the range of 4-5 MHz. When device VDD is 3.0-3.6V, the x4 PLL input frequency must be in the range of 4-6 MHz for both industrial and extended temperature ranges.

### Work around

- 1. Use x8 PLL or x16 PLL mode of operation and set final device clock speed using the POST<1:0> oscillator postscaler control bits (OSCCON<7:6>).

- Use the EC without PLL Clock mode with a suitable clock frequency to obtain the equivalent x4 PLL clock rate.

### 7. Module: Interrupt Controller – Sequential Interrupts

When interrupt nesting is enabled (or NSTDIS (INTCON1<15>) bit is '0'), the following sequence of events will lead to an Address Error trap. The generic terms "Interrupt 1" and "Interrupt 2" are used to represent any two enabled dsPIC30F interrupts.

- 1. Interrupt 1 processing begins.

- 2. Interrupt 1 is negated by user software by one of the following methods:

- CPU IPL is raised to Interrupt 1 IPL level or higher or

- Interrupt 1 IPL is lowered to CPU IPL level or lower or

- Interrupt 1 is disabled (Interrupt 1 IE bit set to '0') or

- Interrupt 1 flag is cleared

- 3. Interrupt 2 with priority higher than Interrupt 1 occurs.

### EXAMPLE 6:

### Work around

The user may disable interrupt nesting or execute a DISI instruction before modifying the CPU IPL or Interrupt 1 setting. A minimum DISI value of 2 is required if the DISI is executed immediately before the CPU IPL or Interrupt 1 is modified, as shown in Example 6. If the MPLAB C30 compiler is being used, one must inspect the Disassembly Listing in the MPLAB IDE file to determine the exact number of cycles to disable level 1-6 interrupts. One may use a large DISI value and then set the DISICNT register to zero, as shown in Example 7. A macro may also be used to perform this task, as shown in Example 8.

| .include   | "p30fxxxx.ir | ac"                                  |

|------------|--------------|--------------------------------------|

|            |              |                                      |

| DISI #2    | i            | ; protect the disable of INT1        |

| BCLR IEC1, | #INT1IE      | ; disable interrupt 1                |

|            | i            | ; next instruction protected by DISI |

### EXAMPLE 7:

```

.include "p30fxxxx.h"

...

__asm__ volatile ("DISI #0x1FFF"); // protect CPU IPL modification

SRbits.IPL = 0x5; // set CPU IPL to 5

DISICNT = 0x0; // remove DISI protection

```

### EXAMPLE 8:

### 8. Module: Using OSC2/RC15 pin for Digital I/O

The port pin, RC15, is multiplexed with the primary oscillator pin, OSC2. When pin RC15 is required for digital input/output, specific bits in the Oscillator Configuration register, FOSC, may be set up as follows:

- FOS<2:0> (FOSC<10:8>) bits configured for LP, LPRC, FRC, ECIO, ERCIO or ECIO w/PLL 4x/8x/16x

- FPR<4:0> (FOSC<4:0>) bits may be configured for ECIO w/PLL 4x/8x/16x

For this revision of silicon, if the RC15 digital I/O port function is desired, the FPR<4:0> bits in the FOSC Configuration register may not be set up for FRC w/PLL 4x/8x/16x modes.

### Work around

None. In future revisions of silicon, port pin RC15 may also be configured for digital I/O when the FPR<4:0> bits in the FOSC Configuration register are set up for FRC w/PLL 4x/8x/16x modes.

### APPENDIX A: REVISION HISTORY

Revision A (11/2004)

Original version of the document.

Revision B (3/2005)

Added silicon issues 6 (PLL) and 7 (Interrupt Controller – Sequential Interrupts).

Revision C (4/2005)

Added silicon issue 8 (Using OSC2/RC15 pin for Digital I/O).

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance and WiperLock are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2005, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOO® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

**Kokomo** Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**San Jose** Mountain View, CA Tel: 650-215-1444 Fax: 650-961-0286

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8676-6200 Fax: 86-28-8676-6599

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR Tel: 852-2401-1200 Fax: 852-2401-3431

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066 China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Qingdao** Tel: 86-532-502-7355 Fax: 86-532-502-7205 ASIA/PACIFIC

India - Bangalore Tel: 91-80-2229-0061 Fax: 91-80-2229-0062

India - New Delhi Tel: 91-11-5160-8631 Fax: 91-11-5160-8632

**Japan - Kanagawa** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Kaohsiung** Tel: 886-7-536-4818

Fax: 886-7-536-4803 Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Taiwan - Hsinchu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

### EUROPE

Austria - Weis Tel: 43-7242-2244-399 Fax: 43-7242-2244-393

**Denmark - Ballerup** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Massy Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Ismaning** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

England - Berkshire Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/01/05