# dsPIC

## 31. března 2005

# Obsah

| 1 | <b>Z</b> áklad           | 3         |

|---|--------------------------|-----------|

|   | 1.1 Úvod                 | 3         |

|   | 1.2 Vnitřní struktura    | 4         |

|   | 1.3 Programátorský model | 5         |

|   | 1.4 Zapojení vývodů      | 6         |

|   | 1.5 Význam vývodů        | 7         |

|   | 1.6 Registry             | 9         |

|   | 1.7 Organizace paměti    | 11        |

|   | 1.8 Přerušení            | 17        |

| 2 | Paměť Flash              | 23        |

| 3 | Porty                    | 24        |

|   | 3.1 Hardware             | 24        |

|   | 3.2 Registry             | 25        |

| 4 | Čítače                   | 26        |

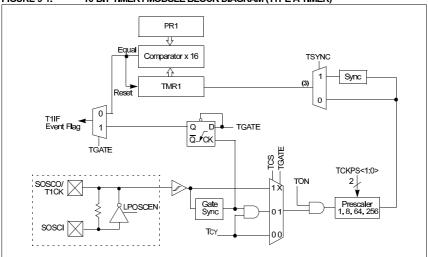

|   | 4.1 Typ A                | 26        |

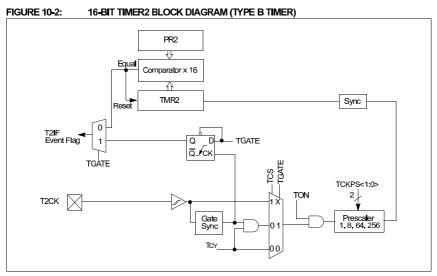

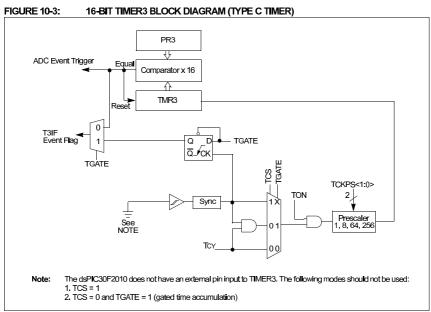

|   | 4.2 Typy B a C           | 27        |

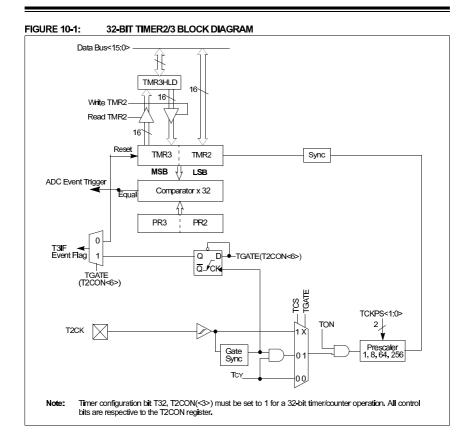

|   | 4.3  32-bitový           | 28        |

|   | 4.4 Řídící registry      | 29        |

| 5 | SPI                      | <b>32</b> |

| _ | 5.1 Struktura            | 32        |

|   | 5.2 Registry             | 33        |

| 6 | UART                     | 37        |

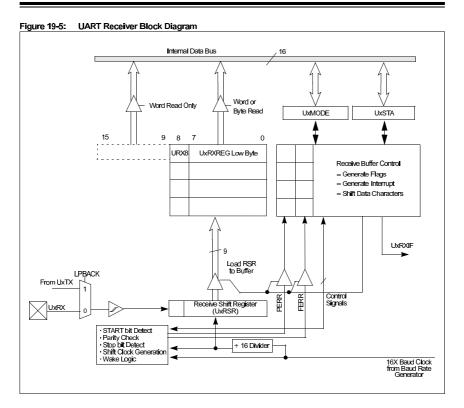

|   | 6.1 Přijímač             | 37        |

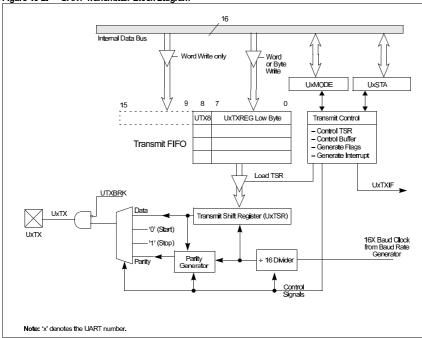

|   | 6.2 Vysílač              | 38        |

|   | 6.3 Registry             | 39        |

| 7 | A/D Převodník            | 45        |

|   | <i>1</i>                 | 45        |

|   | 7.9 Registry             |           |

| 8            | Oscilátor             | 53         |

|--------------|-----------------------|------------|

|              | 8.1 Struktura         |            |

|              | 8.2 Režimy            | 54         |

|              | 8.3 Konfigurace       | 55         |

| 9            | Konfigurační registry | 57         |

| 10           | Instrukční soubor     | <b>5</b> 8 |

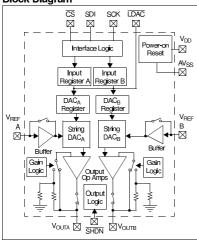

| $\mathbf{A}$ | MCP4921/4922          | 65         |

|              | A.1 Úvod              |            |

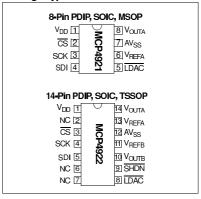

|              | A.2 Vývody            | 66         |

|              | A 3 Rozhraní          | 67         |

### 1 Základ

## 1.1 Úvod

# dsPIC30F2010

## 28-pin dsPIC30F2010 Enhanced Flash 16-bit Digital Signal Controller

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU peripherals, register descriptions and general device functionality, refer to the dsPIC30F Family Reference Manual (DS70046). For more information on the device instruction set and programming, refer to the dsPIC30F Programmer's Reference Manual (DS70030).

#### High-Performance Modified RISC CPU:

- · Modified Harvard architecture

- C compiler optimized instruction set architecture

- 84 base instructions with flexible addressing modes.

- · 24-bit wide instructions, 16-bit wide data path

- 12 Kbytes on-chip Flash program space

- 512 bytes on-chip data RAM

- 1 Kbyte non-volatile data EEPROM

- 16 x 16-bit working register array

- Up to 30 MIPs operation:

- DC to 40 MHz external clock input

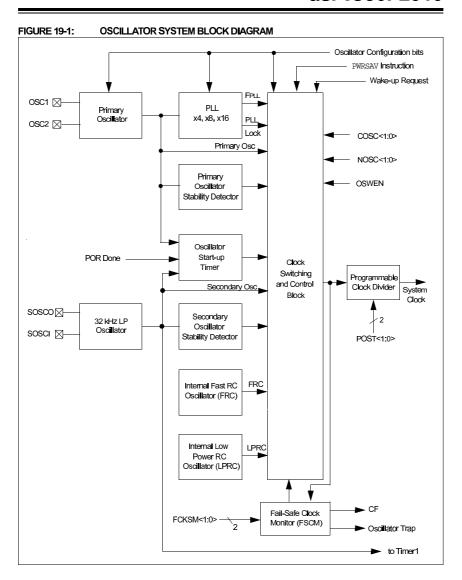

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- 27 interrupt sources

- Three external interrupt sources

- 8 user selectable priority levels for each interrupt

- 4 processor exceptions and software traps

### **DSP Engine Features:**

- Modulo and Bit-Reversed modes

- Two, 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single cycle hardware fractional/ integer multiplier

- Single cycle Multiply-Accumulate (MAC) operation

- · 40-stage Barrel Shifter

- Dual data fetch

#### **Peripheral Features:**

- High current sink/source I/O pins: 25 mA/25 mA

- Three 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- Four 16-bit Capture input functions

- Two 16-bit Compare/PWM output functions

Dual Compare mode available

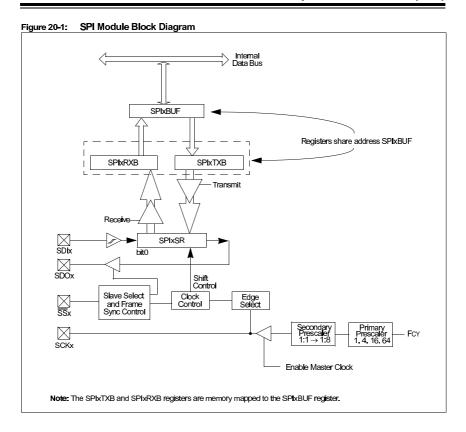

- 3-wire SPI<sup>™</sup> modules (supports 4 Frame modes)

- I<sup>2</sup>C™ module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Addressable UART modules with FIFO buffers

#### **Motor Control PWM Module Features:**

- 6 PWM output channels

- Complementary or Independent Output modes

- Edge and Center Aligned modes

- 4 duty cycle generators

- Dedicated time base with 4 modes

- Programmable output polarity

- Dead time control for Complementary mode

- Manual output control

- Trigger for synchronized A/D conversions

# Quadrature Encoder Interface Module Features:

- Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

#### **Analog Features:**

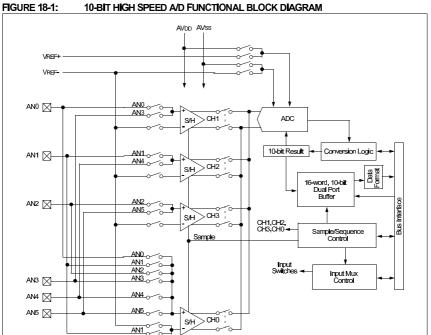

- 10-bit Analog-to-Digital Converter (A/D) with:

- 500 Ksps (for 10-bit A/D) conversion rate

- Six input channels

- Conversion available during Sleep and Idle

- Programmable Brown-out Detection and Reset generation

© 2004 Microchip Technology Inc.

**Preliminary**

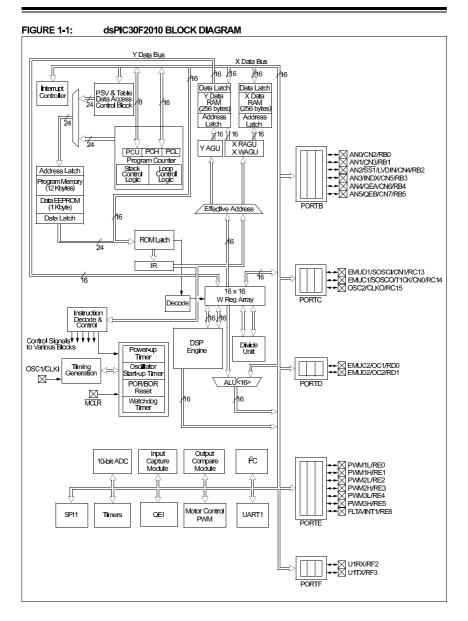

## 1.2 Vnitřní struktura

## dsPIC30F2010

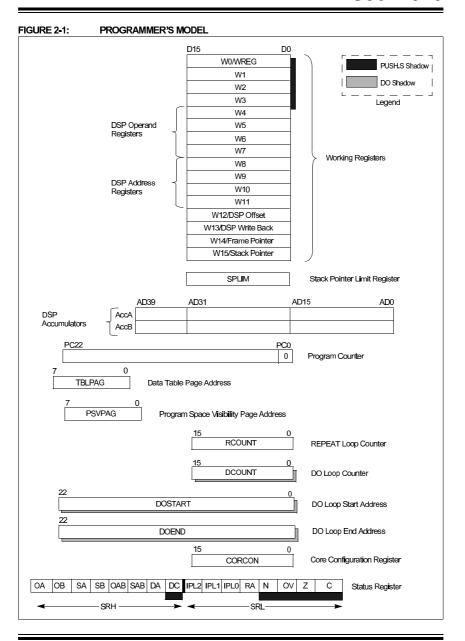

## 1.3 Programátorský model

## dsPIC30F2010

© 2004 Microchip Technology Inc.

**Preliminary**

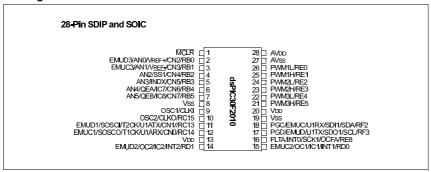

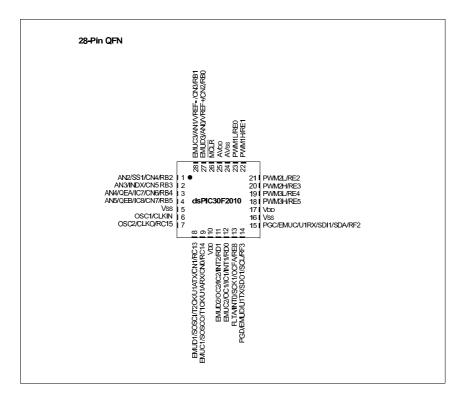

## 1.4 Zapojení vývodů

## dsPIC30F2010

### Pin Diagrams

© 2004 Microchip Technology Inc.

**Preliminary**

## 1.5 Význam vývodů

## dsPIC30F2010

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name              | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                              |

|-----------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN5               |             | Analog         | Analog input channels.                                                                                                                                                                   |

| AVDD                  | Р           | Р              | Positive supply for analog module.                                                                                                                                                       |

| AVss                  | Р           | Р              | Ground reference for analog module.                                                                                                                                                      |

| CLKI                  | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                   |

| CLKO                  | Ö           |                | Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always<br>associated with OSC2 pin function. |

| CN0-CN7               | I           | ST             | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                |

| EMUD                  | <b>I</b> /O | ST             | ICD Primary Communication Channel data input/output pin.                                                                                                                                 |

| EMUC                  | 1/0         | ST             | ICD Primary Communication Channel clock input/output pin.                                                                                                                                |

| EMUD1                 | 1/0         | ST             | ICD Secondary Communication Channel data input/output pin.                                                                                                                               |

| EMUC1                 | 1/0         | ST             | ICD Secondary Communication Channel clock input/output pin.                                                                                                                              |

| EMUD2                 | 1/0         | ST             | ICD Tertiary Communication Channel data input/output pin.                                                                                                                                |

| EMUC2                 | 1/0         | ST             | ICD Tertiary Communication Channel clock input/output pin.                                                                                                                               |

| EMUD3                 | 1/0         | ST             | ICD Quaternary Communication Channel data input/output pin.                                                                                                                              |

| EMUC3                 | I/O         | ST             | ICD Quaternary Communication Channel clock input/output pin.                                                                                                                             |

| IC1, IC2, IC7,<br>IC8 | I           | ST             | Capture inputs. The dsPIC30F2010 has 4 capture inputs. The inputs are numbered for consistency with the inputs on larger device variants.                                                |

| INDX                  | I           | ST             | Quadrature Encoder Index Pulse input.                                                                                                                                                    |

| QEA                   | 1           | ST             | Quadrature Encoder Phase A input in QEI mode.                                                                                                                                            |

|                       |             |                | Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                 |

| QEB                   | ]           | ST             | Quadrature Encoder Phase A input in QEI mode.                                                                                                                                            |

|                       |             |                | Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                 |

| INT0                  | 1           | ST             | External interrupt 0                                                                                                                                                                     |

| INT1                  | 1           | ST             | External interrupt 1                                                                                                                                                                     |

| INT2                  |             | ST             | External interrupt 2                                                                                                                                                                     |

| FLTA                  | j           | ST             | PWM Fault A input                                                                                                                                                                        |

| PWM1L                 | 0           | _              | PWM 1 Low output                                                                                                                                                                         |

| PWM1H                 | 0           | _              | PWM 1 High output                                                                                                                                                                        |

| PWM2L                 | 0           | _              | PWM 2 Low output                                                                                                                                                                         |

| PWM2H                 | 0           | _              | PWM 2 High output                                                                                                                                                                        |

| PWM3L                 | 0           | _              | PWM 3 Low output                                                                                                                                                                         |

| PWM3H                 | 0           | _              | PWM 3 High output                                                                                                                                                                        |

| MCLR                  | <b>I/</b> P | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active low Reset to the device.                                                                                  |

| OCFA                  | J           | ST             | Compare Fault A input (for Compare channels 1, 2, 3 and 4).                                                                                                                              |

| OC1-OC2               | Ö           | _              | Compare outputs.                                                                                                                                                                         |

| OSC1                  | 1           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                                     |

|                       | •           | 217011100      | otherwise.                                                                                                                                                                               |

| OSC2                  | I/O         | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                 |

Legend: CMOS =CMOS compatible input or output Analog= Analog input

ST =Schmitt Trigger input with CMOS levels O= Output

I =Input P = Power

© 2004 Microchip Technology Inc. Preliminary DS70118E-page 7

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IADLE III.                     | PINOL                  | בשט טאוונ           | CRIPTIONS (CONTINUED)                                                                                                                        |

|--------------------------------|------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                       | Pin<br>Type            | Buffer<br>Type      | Description                                                                                                                                  |

| PGD<br>PGC                     | I/O<br>                | ST<br>ST            | In-Circuit Serial Programming data input/output pin.<br>In-Circuit Serial Programming clock input pin.                                       |

| RB0-RB5                        | I/O                    | ST                  | PORTB is a bidirectional I/O port.                                                                                                           |

| RC13-RC14                      | I/O                    | ST                  | PORTC is a bidirectional I/O port.                                                                                                           |

| RD0-RD1                        | I/O                    | ST                  | PORTD is a bidirectional I/O port.                                                                                                           |

| RE0-RE5,<br>RE8                | I/O                    | ST                  | PORTE is a bidirectional I/O port.                                                                                                           |

| RF2, RF3                       | I/O                    | ST                  | PORTF is a bidirectional I/O port.                                                                                                           |

| SCK1<br>SDI1<br>SDO1<br>SS1    | I/O<br> <br> <br> <br> | ST<br>ST<br>—<br>ST | Synchronous serial clock input/output for SPI™ #1. SPI #1 Data In. SPI #1 Data Out. SPI #1 Slave Synchronization.                            |

| SCL<br>SDA                     | I/O<br>I/O             | ST<br>ST            | Synchronous serial clock input/output for I <sup>2</sup> C.<br>Synchronous serial data input/output for I <sup>2</sup> C.                    |

| SOSCO<br>SOSCI                 | 0<br>                  | ST/CMOS             | 32 kHz low power oscillator crystal output. 32 kHz low power oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise. |

| T1CK<br>T2CK                   | l<br>I                 | ST<br>ST            | Timer1 external clock input.<br>Timer2 external clock input.                                                                                 |

| U1RX<br>U1TX<br>U1ARX<br>U1ATX | <br>  0<br>  0         | ST<br>—<br>ST<br>—  | UART1 Receive. UART1 Transmit. UART1 Alternate Receive. UART1 Alternate Transmit.                                                            |

| VDD                            | Р                      | _                   | Positive supply for logic and I/O pins.                                                                                                      |

| Vss                            | Р                      | _                   | Ground reference for logic and I/O pins.                                                                                                     |

| VREF+                          | I                      | Analog              | Analog Voltage Reference (High) input.                                                                                                       |

| VREF-                          | I                      | Analog              | Analog Voltage Reference (Low) input.                                                                                                        |

|                                |                        |                     |                                                                                                                                              |

Legend: CMOS =CMOS compatible input or output Analog= Analog input

ST =Schmitt Trigger input with CMOS levels O= Output

I =Input P = Over

DS70118E-page 8 Preliminary © 2004 Microchip Technology Inc.

# 1.6 Registry

# dsPIC30F2010

| TABLE 3-3: |                       | ORE RE | <b>CORE REGISTER MAP</b> | MAP    |                           |         | •        |       |           |       |            |          |             |       |          |       |                      |

|------------|-----------------------|--------|--------------------------|--------|---------------------------|---------|----------|-------|-----------|-------|------------|----------|-------------|-------|----------|-------|----------------------|

| SFR Name   | Address<br>(Home)     | Bit 15 | Břt 14                   | Bit 13 | Bit 12                    | Bit 11  | Bit 10   | Bit 9 | Bit 8     | Bit 7 | Bit 6      | Břt 5 B  | Bit 4 Bit 3 | Bit 2 | Bit 1    | Bit 0 | Reset State          |

| WO         | 0000                  |        |                          |        |                           |         |          |       | WO / WREG | 55    |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W1         | 000                   |        |                          |        |                           |         |          |       | W         |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W2         | 4000                  |        |                          |        |                           |         |          |       | WZ        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W3         | 9000                  |        |                          |        |                           |         |          |       | W3        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W4         | 8000                  |        |                          |        |                           |         |          |       | W4        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W5         | A000                  |        |                          |        |                           |         |          |       | SW        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| We         | 000C                  |        |                          |        |                           |         |          |       | We        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W7         | 3000                  |        |                          |        |                           |         |          |       | ZW        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W8         | 0100                  |        |                          |        |                           |         |          |       | W8        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| 6M         | 0012                  |        |                          |        |                           |         |          |       | 6W        |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W10        | 4100                  |        |                          |        |                           |         |          |       | W10       |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W11        | 9100                  |        |                          |        |                           |         |          |       | W11       |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W12        | 8100                  |        |                          |        |                           |         |          |       | W12       |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W13        | 001A                  |        |                          |        |                           |         |          |       | W13       |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W14        | 001C                  |        |                          |        |                           |         |          |       | W14       |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| W15        | 001E                  |        |                          |        |                           |         |          |       | W15       |       |            |          |             |       |          |       | 0000 T000 0000 0000  |

| SPLIM      | 0020                  |        |                          |        |                           |         |          |       | SPLIM     |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| ACCAL      | 2200                  |        |                          |        |                           |         |          |       | ACCAL     |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| ACCAH      | 0024                  |        |                          |        |                           |         |          |       | ACCAH     | _     |            |          |             |       |          |       | 0000 0000 0000 0000  |

| ACCAU      | 9200                  |        |                          | SignE  | Sign-Extension (ACCA<39>) | 4CCA<39 | ^        |       |           |       |            |          | ACCAU       |       |          |       | 0000 0000 0000 0000  |

| ACCBL      | 8700                  |        |                          |        |                           |         |          |       | ACCBL     |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| ACCBH      | 002A                  |        |                          |        |                           |         |          |       | ACCBH     | _     |            |          |             |       |          |       | 0000 0000 0000 0000  |

| ACCBU      | 002C                  |        |                          | Sign   | Sign-Extension (ACCB<39>  | 4CCB<39 | ×        |       |           |       |            |          | ACCBU       |       |          |       | 0000 0000 0000 0000  |

| PCL        | 3200                  |        |                          |        |                           |         |          |       | PCL       |       |            |          |             |       |          |       | 0000 0000 0000 0000  |

| PCH        | 0030                  | I      | -                        | I      | I                         | ı       | 1        | ı     | ı         | I     |            |          | PCH         |       |          |       | 0000 0000 0000 0000  |

| TBLPAG     | 0032                  | ı      | -                        | ı      | ı                         | ı       | ı        | ı     | 1         |       |            |          | TBLPAG      |       |          |       | 0000 0000 0000 0000  |

| PSVPAG     | 0034                  | I      | -                        | I      | I                         | ı       | 1        | 1     | I         |       |            |          | PSVPAG      |       |          |       | 0000 0000 0000 0000  |

| RCOUNT     | 9800                  |        |                          |        |                           |         |          |       | RCOUNT    | _     |            |          |             |       |          |       | mana mana mana mana  |

| DCOUNT     | 800                   |        |                          |        |                           |         |          |       | DCOUNT    | _     |            |          |             |       |          |       | mmn mmn mmn mmn      |

| DOSTARTL   | O03A                  |        |                          |        |                           |         |          | ă     | DOSTARTL  |       |            |          |             |       |          | 0     | omn mm mm nmm        |

| DOSTARTH   | 2600                  | ı      | -                        | I      | ı                         | ı       | ı        | ı     | ı         | ı     |            |          | DOSTARTH    | Ŧ     |          |       | nmn nnno 0000 0000   |

| DOENDL     | 003E                  |        |                          |        |                           |         |          | Z     | DOENDL    |       |            |          |             |       |          | 0     | ממוח חחתו חחתו חותום |

| DOENDH     | 0040                  | I      | I                        | I      | I                         | ı       | I        | I     | I         | ı     |            |          | DOENDH      | _     | i        |       | 0000 0000 0nnn nnnn  |

| SR         | 0042                  | OA     | <b>8</b> 0               | ΑS     | SB                        | OAB     | SAB      | DA    | 20        | IPL2  | IPL1       | IPL0 F   | RA N        | Ø     | Z        | ပ     | 0000 0000 0000 0000  |

| CORCON     | 4400                  | I      | I                        | I      | SN                        | EDT     | D1.2     | DL1   | DL0       | SATA  | SATB SATDW | _        | ACCSAT IPL3 | PSV   | SND<br>D | ш     | 0000 0000 0010 0000  |

| MODCON     | 0046                  | XMODEN | XMODEN YMODEN            | I      | ı                         |         | BWM<3:0> | 43:0⊳ |           |       | YWM        | YWM<3:0> |             | XW    | XVM<3:0> |       | 0000 0000 0000 0000  |

| n :pueßen  | u = uninitialized bit | ed bit |                          |        |                           |         |          |       |           |       |            |          |             |       |          |       |                      |

DS70118E-page 28

Preliminary

| IABLE 3-3: CORE REGISTER MAP (CONTINUED) | ر<br>د                | SKI Z  | HISE I                                   | )<br>APE > |        |        |        |       |           |               |       |       |       |     |             |       |                     |

|------------------------------------------|-----------------------|--------|------------------------------------------|------------|--------|--------|--------|-------|-----------|---------------|-------|-------|-------|-----|-------------|-------|---------------------|

| SFR Name (Home)                          | Address<br>(Home)     | Bit 15 | Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9 | 9 Bit 8 E | 3#.7          | Bit 6 | Bit 5 | Bit 4 | B#3 | Bit 2 Bit 1 | Bit 0 | Reset State         |

| XMODSRT                                  | 0048                  |        |                                          |            |        |        |        | XX    | XS<15:1>  |               |       |       |       |     |             | 0     | oran rara nran nara |

| MODEND                                   | 004A                  |        |                                          |            |        |        |        | Ÿ     | XE<15:1>  |               |       |       |       |     |             | 1     | penn mma mma nama   |

| MODSRT                                   | 004C                  |        |                                          |            |        |        |        | ΥŞ    | YS<15:1>  |               |       |       |       |     |             | 0     | oran rara naan nara |

| YMODEND                                  | 004E                  |        |                                          |            |        |        |        | 炡     | YE<15:1>  |               |       |       |       |     |             | 1     | mana mma mma mma    |

| (BREV                                    | 0020                  | BREN   |                                          |            |        |        |        |       | XE        | XB<14:0>      |       |       |       |     |             |       | aran man aran nara  |

| DISICNT                                  | 0062                  | I      | I                                        |            |        |        |        |       |           | DISICNT<13:0> | <130> |       |       |     |             |       | 0000 0000 0000 0000 |

| n :pueßer                                | u = uninitialized bit | æd bit |                                          |            |        |        |        |       |           |               |       |       |       |     |             | -     |                     |

|                                          |                       |        |                                          |            |        |        |        |       |           |               |       |       |       |     |             |       |                     |

Note: Refer to dsPIC30F Family Reference Manual (DS70046) for descriptions of register bit fields.

© 2004 Microchip Technology Inc.

Preliminary

## 1.7 Organizace paměti

## dsPIC30F2010

### 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the dsPIC30F Family Reference Manual (DS70046). For more information on the device instruction set and programming, refer to the dsPIC30F Programmer's Reference Manual (DS70030).

#### 3.1 Program Address Space

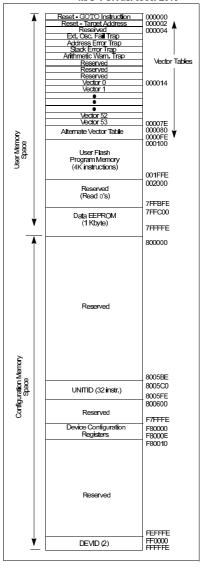

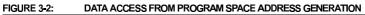

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space, as defined by Table 3-1. Note that the program space address is incremented by two between successive program words, in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE), for all accesses other than TBLRD/TBLWT, which use TBLPAG</>

To determine user or configuration space access. In Table 3-1, Read/Write instructions, bit 23 allows access to the Device ID, the User ID and the configuration bits. Otherwise, bit 23 is always clear.

Note: The address map shown in Figure 3-1 is conceptual, and the actual memory configuration may vary across individual devices depending on available memory.

FIGURE 3-1: PROGRAM SPACE MEMORY MAP FOR dsPiC30F2010

© 2004 Microchip Technology Inc.

**Preliminary**

TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

| A Trus                   | Access                           |      | Progra    | m Space A | ddress         |      |

|--------------------------|----------------------------------|------|-----------|-----------|----------------|------|

| Access Type              | Space                            | <23> | <22:16>   | <15>      | <14:1>         | <0>  |

| Instruction Access       | User                             | 0    |           | PC<22:1>  |                | 0    |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)          | TBL  | PAG<7:0>  |           | Data EA <15:0> |      |

| TBLRD/TBLWT              | Configuration<br>(TBLPAG<7> = 1) | TBL  | .PAG<7:0> |           | Data EA <15:0> |      |

| Program Space Visibility | User                             | 0    | PSVPAG<   | :7:0>     | Data EA <1     | 4:0> |

DS70118E-page 20 Preliminary © 2004 Microchip Technology Inc.

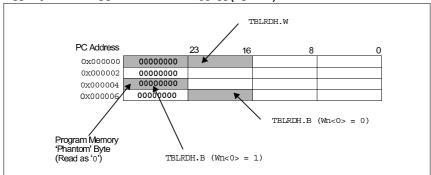

#### DATA ACCESS FROM PROGRAM 3.1.1 MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

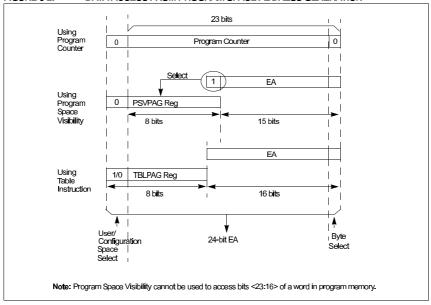

There are two methods by which program space can be accessed; via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the LS Word of any address within program space, without going through data space. The TBI RDH and TBI WITH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresse Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the LS Data Word. and TBLRDH and TBLWTH access the space which contains the MS Data Byte.

Figure 3-2 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of Table Instructions are provided to move byte or word sized data to and from program space.

- TBLRDL: Table Read Low Word: Read the LS Word of the program address;

- P<15:0> maps to D<15:0>

- Byte: Read one of the LS Bytes of the program address;

- P<7:0> maps to the destination byte when byte select = 0

- P<15:8> maps to the destination byte when byte select = 1.

- TBLWTL: Table Write Low (refer to Section 6.0 for details on Flash Programming).

- TBLRDH: Table Read High

Word: Read the MS Word of the program address:

- P<23:16> maps to D<7:0>; D<15:8> always be = 0.

- Byte: Read one of the MS Bytes of the program

- P<23:16> maps to the destination byte when byte select = o;

- The destination byte will always be = 0 when byte select = 1.

- TBLWTH: Table Write High (refer to Section 6.0 for details on Flash Programming).

FIGURE 3-3: PROGRAM DATA TABLE ACCESS (LS WORD)

FIGURE 3-4: PROGRAM DATA TABLE ACCESS (MS BYTE)

# 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space, without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MS bit of the data space EA is set and program space visibility is enabled, by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in Section 24, DSP Engine.

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 3-5), only the lower 16-bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. Refer to the Programmer's Reference Manual (DS70030) for details on instruction encoding.

Note that by incrementing the PC by 2 for each program memory word, the LS 15 bits of data space addresses directly map to the LS 15 bits in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-5.

Note: PSV access is temporarily disabled during Table Reads/Writes.

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions will require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand pre-fetch

- MOV instructions

- MOV.D instructions

- All other instructions will require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a REPEAT loop:

- The following instances will require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop will allow the instruction, accessing data using PSV, to execute in a single cycle.

DS70118E-page 22

Preliminary

DATA SPACE WINDOW INTO PROGRAM SPACE OPERATION FIGURE 3-5: Data Space Program Space 0x100100 0x0000 PSVPAG(1) EA < 15 > = 00x00 Data 16 Space 0x8000ĒΑ Address EA<15> = 1 0x001200 Concatenation 23 Upper half of Data Space is mapped ◀ into Program Space OXFFFF 0x001FFE BSET CORCON,#2 ; PSV bit set #0x00, W0 W0, PSVPAG MOV ; Set PSVPAG register MOV MOV 0x9200, W0 ; Access program memory location Data Read ; using a data space access Note: PSVPAG is an 8-bit register, containing bits <22:15> of the program space address (i.e., it defines the page in program space to which the upper half of data space is being mapped).

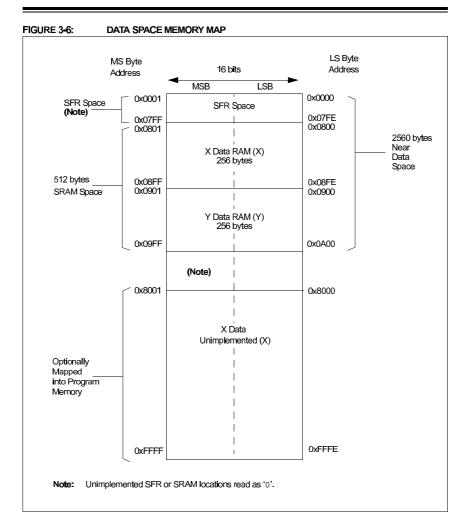

### 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MaC class of instructions, the X block consists of the 256 byte data address space (including all Y addresses). When executing one of the MaC class of instructions, the X block consists of the 256 bytes data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MaC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

A data space memory map is shown in Figure 3-6.

DS70118E-page 24 Preliminary © 2004 Microchip Technology Inc.

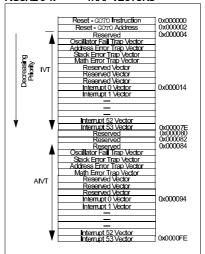

#### 5.0 INTERRUPTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the dsPIC30F Family Reference Manual (DS70046). For more information on the device instruction set and programming, refer to the dsPIC30F Programmer's Reference Manual (DS70030).

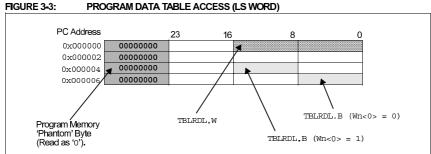

The dsPIC30F2010 has 24 interrupt sources and 4 processor exceptions (traps), which must be arbitrated based on a priority scheme.

The CPU is responsible for reading the Interrupt Vector Table (IVT) and transferring the address contained in the interrupt vector to the program counter. The interrupt vector is transferred from the program data bus into the program counter, via a 24-bit wide multiplexer on the input of the program counter.

The Interrupt Vector Table (IVT) and Alternate Interrupt Vector Table (AIVT) are placed near the beginning of program memory (0x000004). The IVT and AIVT are shown in Figure 5-1.

The interrupt controller is responsible for preprocessing the interrupts and processor exceptions, prior to their being presented to the processor core. The peripheral interrupts and traps are enabled, prioritized and controlled using centralized special function registers:

- IFSO<15:0>, IFS1<15:0>, IFS2<15:0>

All interrupt request flags are maintained in these three registers. The flags are set by their respective peripherals or external signals, and they are cleared via software.

- IECO<15:0>, IEC1<15:0>, IEC2<15:0>

All interrupt enable control bits are maintained in these three registers. These control bits are used to individually enable interrupts from the peripherals or external signals.

- IPC0<15:0>... IPC11<7:0>

The user assignable priority level associated with each of these interrupts is held centrally in these twelve registers.

- IPL<3:0> The current CPU priority level is explicitly stored in the IPL bits. IPL<3> is present in the CORCON register, whereas IPL<2:0> are present in the status register (SR) in the processor core.

INTCON1<15:0>, INTCON2<15:0>

Global interrupt control functions are derived from these two registers. INTCON1 contains the control and status flags for the processor exceptions. The INTCON2 register controls the external interrupt request signal behavior and the use of the alternate vector table.

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

All interrupt sources can be user assigned to one of 7 priority levels, 1 through 7, via the IPCx registers. Each interrupt source is associated with an interrupt vector, as shown in Figure 5-1. Levels 7 and 1 represent the highest and lowest maskable priorities, respectively.

**Note:** Assigning a priority level of 0 to an interrupt source is equivalent to disabling that interrupt.

If the NSTDIS bit (INTCON1<15>) is set, nesting of interrupts is prevented. Thus, if an interrupt is currently being serviced, processing of a new interrupt is prevented, even if the new interrupt is of higher priority than the one currently being serviced.

Note: The IPL bits become read-only whenever the NSTDIS bit has been set to '1'.

Certain interrupts have specialized control bits for features like edge or level triggered interrupts, interrupt-on-change, etc. Control of these features remains within the peripheral module which generates the interrupt.

The DISI instruction can be used to disable the processing of interrupts of priorities 6 and lower for a certain number of instructions, during which the DISI bit (INTCON2<14>) remains set.

When an interrupt is serviced, the PC is loaded with the address stored in the vector location in Program Memory that corresponds to the interrupt. There are 63 different vectors within the IVT (refer to Figure 5-1). These vectors are contained in locations 0x000004 through 0x0000FE of program memory (refer to Figure 5-1). These locations contain 24-bit addresses, and in order to preserve robustness, an address error trap will take place should the PC attempt to fetch any of these words during normal execution. This prevents execution of random data as a result of accidentally decrementing a PC into vector space, accidentally mapping a data space address into vector space, or the PC rolling over to 0x000000 after reaching the end of implemented program memory space. Execution of a GOTO instruction to this vector space will also generate an address error trap.

© 2004 Microchip Technology Inc.

**Preliminary**

### 5.1 Interrupt Priority

The user assignable Interrupt Priority (IP<2:0>) bits for each individual interrupt source are located in the LS 3-bits of each nibble, within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user selectable priority levels start at   |

|-------|------------------------------------------------|

|       | 0, as the lowest priority, and level 7, as the |

|       | highest priority.                              |

Since more than one interrupt request source may be assigned to a specific user specified priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority" and is final.

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 5-1 lists the interrupt numbers and interrupt sources for the dsPIC devices and their associated vector numbers.

Note 1: The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

2: The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels implies that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PLVD (Low Voltage Detect) can be given a priority of 7. The INTO (external interrupt 0) may be assigned to priority level 1, thus giving it a very low effective priority.

TABLE 5-1: dsPIC30F2010 INTERRUPT VECTOR TABLE

| INT<br>Number | Vector<br>Number    | Interrupt Source                         |

|---------------|---------------------|------------------------------------------|

| Highest N     | atura <b>l</b> Orde |                                          |

| 0             | 8                   | INT0 - External Interrupt 0              |

| 1             | 9                   | IC1 - Input Capture 1                    |

| 2             | 10                  | OC1 - Output Compare 1                   |

| 3             | 11                  | T1 - Timer 1                             |

| 4             | 12                  | IC2 - Input Capture 2                    |

| 5             | 13                  | OC2 - Output Compare 2                   |

| 6             | 14                  | T2 - Timer 2                             |

| 7             | 15                  | T3 - Timer 3                             |

| 8             | 16                  | SPI1                                     |

| 9             | 17                  | U1RX - UART1 Receiver                    |

| 10            | 18                  | U1TX - UART1 Transmitter                 |

| 11            | 19                  | ADC - ADC Convert Done                   |

| 12            | 20                  | NVM - NVM Write Complete                 |

| 13            | 21                  | SI2C - I <sup>2</sup> C Slave Interrupt  |

| 14            | 22                  | MI2C - I <sup>2</sup> C Master Interrupt |

| 15            | 23                  | Input Change Interrupt                   |

| 16            | 24                  | INT1 - External Interrupt 1              |

| 17            | 25                  | IC7 - Input Capture 7                    |

| 18            | 26                  | IC8 - Input Capture 8                    |

| 19            | 27                  | Reserved                                 |

| 20            | 28                  | Reserved                                 |

| 21            | 29                  | Reserved                                 |

| 22            | 30                  | Reserved                                 |

| 23            | 31                  | INT2 - External Interrupt 2              |

| 24            | 32                  | Reserved                                 |

| 25            | 33                  | Reserved                                 |

| 26            | 34                  | Reserved                                 |

| 27            | 35                  | Reserved                                 |

| 28            | 36                  | Reserved                                 |

| 29            | 37                  | Reserved                                 |

| 30            | 38                  | Reserved                                 |

| 31            | 39                  | Reserved                                 |

| 32            | 40                  | Reserved                                 |

| 33            | 41                  | Reserved                                 |

| 34            | 42                  | Reserved                                 |

| 35            | 43                  | Reserved                                 |

| 36            | 44                  | INT3 - External Interrupt 3              |

| 37            | 45                  | Reserved                                 |

| 38            | 46                  | Reserved                                 |

| 39            | 47                  | PWM - PWM Period Match                   |

| 40            | 48                  | QEI - QEI Interrupt                      |

| 41            | 49                  | Reserved                                 |

| 42            | 50                  | Reserved                                 |

| 43            | 51                  | FLTA - PWM Fault A                       |

| 44            | 52                  | Reserved                                 |

| 45-53         | 53-61               | Reserved                                 |

| Lowest Na     | atural Orde         | r Priority                               |

DS70118E-page 38 Preliminary

### 5.2 Reset Sequence

A Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The processor initializes its registers in response to a Reset, which forces the PC to zero. The processor then begins program execution at location 0x000000. A GOTO instruction is stored in the first program memory location, immediately followed by the address target for the GOTO instruction. The processor executes the GOTO to the specified address and then begins operation at the specified target (start) address.

#### 5.2.1 RESET SOURCES

In addition to External Reset and Power-on Reset (POR), there are 6 sources of error conditions which 'trap' to the Reset vector.

- Watchdog Time-out: The watchdog has timed out, indicating that the processor is no longer executing the correct flow of code.

- Uninitialized W Register Trap:

An attempt to use an uninitialized W register as an address pointer will cause a Reset.

- Illegal Instruction Trap:

Attempted execution of any unused opcodes will result in an illegal instruction trap. Note that a fetch of an illegal instruction does not result in an illegal instruction trap if that instruction is flushed prior to execution due to a flow change.

- Brown-out Reset (BOR):

A momentary dip in the power supply to the device has been detected, which may result in malfunction.

- Trap Lockout:

Occurrence of multiple Trap conditions simultaneously will cause a Reset.

#### 5.3 Traps

Traps can be considered as non-maskable interrupts indicating a software or hardware error, which adhere to a predefined priority as shown in Figure 5-1. They are intended to provide the user a means to correct erroneous operation during debug and when operating within the application.

Note: If the user does not intend to take corrective action in the event of a trap error condition, these vectors must be loaded with the address of a default handler that simply contains the RESET instruction. If, on the other hand, one of the vectors containing an invalid address is called, an

Note that many of these trap conditions can only be detected when they occur. Consequently, the questionable instruction is allowed to complete prior to trap exception processing. If the user chooses to recover from the error, the result of the erroneous action that caused the trap may have to be corrected.

address error trap is generated.

There are 8 fixed priority levels for traps: Level 8 through Level 15, which implies that the IPL3 is always set during processing of a trap.

If the user is not currently executing a trap, and he sets the IPL<3:0> bits to a value of '0111' (Level 7), then all interrupts are disabled, but traps can still be processed.

#### 5.3.1 TRAP SOURCES

The following traps are provided with increasing priority. However, since all traps can be nested, priority has little effect.

Math Error Trap:

The Math Error trap executes under the following three circumstances:

- Should an attempt be made to divide by zero, the divide operation will be aborted on a cycle boundary and the trap taken.

- If enabled, a Math Error trap will be taken when an arithmetic operation on either accumulator A or B causes an overflow from bit 31 and the accumulator guard bits are not utilized.

- If enabled, a Math Error trap will be taken when an arithmetic operation on either accumulator A or B causes a catastrophic overflow from bit 39 and all saturation is disabled.

- If the shift amount specified in a shift instruction is greater than the maximum allowed shift amount, a trap will occur.

© 2004 Microchip Technology Inc.

**Preliminary**

#### Address Error Trap:

This trap is initiated when any of the following circumstances occurs:

- 1. A misaligned data word access is attempted.

- A data fetch from our unimplemented data memory location is attempted.

- A data access of an unimplemented program memory location is attempted.

- An instruction fetch from vector space is attempted.

Note: In the MAC class of instructions, wherein the data space is split into X and Y data space, unimplemented X space includes all of Y space, and unimplemented Y space includes all of X space.

- Execution of a "BRA #literal" instruction or a "GOTO #literal" instruction, where literal is an unimplemented program memory address.

- Executing instructions after modifying the PC to point to unimplemented program memory addresses. The PC may be modified by loading a value into the stack and executing a RETURN instruction.

#### Stack Error Trap:

This trap is initiated under the following conditions:

- The stack pointer is loaded with a value which is greater than the (user programmable) limit value written into the SPLIM register (stack overflow).

- 2. The stack pointer is loaded with a value which is less than 0x0800 (simple stack underflow).

#### Oscillator Fail Trap:

This trap is initiated if the external oscillator fails and operation becomes reliant on an internal RC backup.

#### 5.3.2 HARD AND SOFT TRAPS

It is possible that multiple traps can become active within the same cycle (e.g., a misaligned word stack write to an overflowed address). In such a case, the fixed priority shown in Figure 5-1 is implemented, which may require the user to check if other traps are pending, in order to completely correct the fault.

'Soft traps include exceptions of priority level 8 through level 11, inclusive. The arithmetic error trap (level 11) falls into this category of traps.

'Hard' traps include exceptions of priority level 12 through level 15, inclusive. The address error (level 12), stack error (level 13) and oscillator error (level 14) traps fall into this category.

Each hard trap that occurs must be acknowledged before code execution of any type may continue. If a lower priority hard trap occurs while a higher priority trap is pending, acknowledged, or is being processed, a hard trap conflict will occur.

The device is automatically Reset in a hard trap conflict condition. The TRAPR status bit (RCON<15>) is set when the Reset occurs, so that the condition may be detected in software.

FIGURE 5-1: TRAP VECTORS

DS70118E-page 40 Preliminary

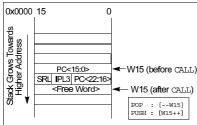

#### 5.4 Interrupt Sequence

All interrupt event flags are sampled in the beginning of each instruction cycle by the IFSx registers. A pending interrupt request (IRQ) is indicated by the flag bit being equal to a '1' in an IFSx register. The IRQ will cause an interrupt to occur if the corresponding bit in the interrupt enable (IECx) register is set. For the remainder of the instruction cycle, the priorities of all pending interrupt requests are evaluated.

If there is a pending IRQ with a priority level greater than the current processor priority level in the IPL bits, the processor will be interrupted.

The processor then stacks the current program counter and the low byte of the processor status register (SRL), as shown in Figure 5-2. The low byte of the status register contains the processor priority level at the time, prior to the beginning of the interrupt cycle. The processor then loads the priority level for this interrupt into the status register. This action will disable all lower priority interrupts until the completion of the Interrupt Service Routine.

FIGURE 5-2: INTERRUPT STACK FRAME

Note 1: The user can always lower the priority level by writing a new value into SR. The Interrupt Service Routine must clear the interrupt flag bits in the IFSx register before lowering the processor interrupt priority, in order to avoid recursive interrupts.

2: The IPL3 bit (CORCON<3>) is always clear when interrupts are being processed. It is set only during execution of trans

The RETFIE (Return from Interrupt) instruction will unstack the program counter and status registers to return the processor to its state prior to the interrupt sequence.

#### 5.5 Alternate Vector Table

In Program Memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 5-1. Access to the Alternate Vector Table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment, without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

#### 5.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the PUSH.S and POP.S instructions only.

When the processor vectors to an interrupt, the PUSH.s instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt, if the higher priority ISR uses fast context saving.

### 5.7 External Interrupt Requests

The interrupt controller supports five external interrupt request signals, INT0-INT4. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has five bits, INT0EP-INT4EP, that select the polarity of the edge detection circuitry.

### 5.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake up the processor from either Sleep or Idle modes, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor will wake-up from Sleep or Idle and begin execution of the Interrupt Service Routine (ISR) needed to process the interrupt request.

© 2004 Microchip Technology Inc.

**Preliminary**

| TABLE 5-2:   | 5-2   | Ĕ                     | ERRUF  | oT CO      | MTROL  | LER F  | INTERRUPT CONTROLLER REGISTER MAP | ER MA       | یَه   |        |       |             |         |         |           |                |        |                           |

|--------------|-------|-----------------------|--------|------------|--------|--------|-----------------------------------|-------------|-------|--------|-------|-------------|---------|---------|-----------|----------------|--------|---------------------------|

| SFR<br>Name  | ADR   | Bit 15                | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10                            | Bit 9       | Bit 8 | Bit 7  | Bit 6 | Bit 5       | Bit 4   | Bit 3   | Bit 2     | Bit 1          | Bit 0  | Reset State               |

| INTCON1 0080 | 000   | NSTDIS                | I      | ı          | I      | I      | OWATE                             | OVBTE       | COVIE | ı      | ı     | I           | MATHERR | ADDRERR |           | STKERR OSCFAIL | ı      | 0000 0000 0000 0000       |

| INTCONZ      | 0082  | ALTIVT                | ı      | ı          | ı      | ı      | ı                                 | ı           | ı     | J      | ı     | ı           | ı       |         | INTZEP    | INTIEP         | INTOEP | 0000 0000 0000 0000       |

| IFS0         | 0084  | GNIF                  | MIZCIF | SECIF      | NVMIF  | ADIF   | UTTXIF UTRXIF                     | U1RXIF      | SPINE | T3IF   | T2IF  | OCZIF       | IC2IF   | 111F    | OC1IF     | ICIIE          | INTOIF | NTOIF 0000 0000 0000 0000 |

| FS1          | 9800  | ı                     | ı      | ı          | ı      | ı      | ı                                 | ı           | ı     | INTZIF | ı     | ı           | ı       | -       | 188F      | IC7IF          | INT1IF | 0000 0000 0000 0000       |

| FS2          | 9800  | I                     | I      | ı          | I      | PLTAIF | I                                 | I           | SEIIF | PWMIF  | I     | I           | I       | I       | I         | I              | I      | 0000 0000 0000 0000       |

| ECS          | 008C  | CNIE                  | MI2CIE | SIZCIE     | NAMIE  | ADIE   | UITXIE                            | UIRXIE      | SPINE | T3IE   | TZIE  | OC2IE       | ICSIE   | 111E    | OC1E      | ICIE           | INTOIE | 0000 0000 0000 0000       |

| EG           | 3800  | I                     | I      | ı          | I      | I      | I                                 | I           | I     | INT2IE | I     | I           | I       | I       | <u>88</u> | IC7IE          | INTIE  | 0000 0000 0000 0000       |

| EC2          | 0600  | ı                     | 1      | ı          | ı      | FLTAIE | ı                                 | ı           | OEIIE | PWMIE  | ı     | ı           | ı       | -       | I         | ı              | 1      | 0000 0000 0000 0000       |

| <u>B</u>     | 0094  | ı                     | _      | 11P<2:0>   |        | ı      | 0                                 | OC1IP<2:0>  | ^     | ı      |       | C1  P<2:0>  | Ą       | -       |           | NT0IP<2:0>     |        | оото оото оото оото       |

| <u>2</u>     | 9600  | ı                     | Ţ      | F31P<2:0>  |        | ı      | ų.                                | T2IP<2:0>   |       | ı      |       | 40:Z>dR2:0> | Ą.      | -       |           | IC2IP<2:0>     |        | 00т0 00т0 00т0 00т0       |

| PC2          | 8600  | 1                     | 4      | ADIP<2:0>  |        | -      | Ò                                 | U1TXIP<2:0> | ٨     | 1      | ر     | JIRXIP<2:0> | 5:0⊳    | -       | •,        | SPI1IP<2:0>    |        | 0010 0010 0010 0010       |

| <u>ප</u>     | O09A  | ı                     | J      | QNIP<2:0>  |        | ı      | X                                 | MIZCIP<2:0> | ٨     | ı      |       | SI2CIP<2:0> | 40:     | -       | _         | NVMIP<2:0>     |        | 00т0 00т0 00т0 00т0       |

| <u>P</u> 2   | 000C  | ı                     | ı      | ı          | ı      | ı      | _                                 | C8IP<2:0>   |       | ı      |       | IC7IP<2:0>  | ₽.      |         |           | INT1IP<2:0>    |        | 0010 0010 0010 0010       |

| <u>P</u> C5  | 3600  | ı                     | 2      | NT2/P<2:0> | ۸      | ı      | ı                                 | ı           | ı     | ı      | ı     | ı           | ı       | -       | I         | ı              | 1      | 0000 0000 0000 0010       |

| <u>B</u>     | 00A0  | ı                     | ı      | ı          | ı      | ı      | ĺ                                 | ı           | ı     | ı      | ı     | ı           | ı       | ı       | I         | I              | ı      | 0000 0000 0000 0000       |

| PC7          | 00A2  | ı                     | 1      | ı          | -      | ı      | ı                                 | ı           | ı     | ı      | 1     | ı           | 1       | -       | I         | I              | I      | 0000 0000 0000 0000       |

| PC8          | 00A4  | I                     | ı      | ı          | I      | ı      | ı                                 | -           | ı     | ı      | ı     | ı           | ı       |         | I         | I              | I      | 0000 0000 0000 0000       |

| PC9          | 00A6  | ı                     | Д      | PWMIP<2:0> | Δ      | ı      | ı                                 | ı           | ı     | ı      | ı     | ı           | -       |         | I         | l              | I      | 0000 0000 0000 0000       |

| IPC10        | 00A8  | I                     | Н      | RTAIP<2:0> | ^      | ı      | ı                                 | -           | ı     | ı      | ı     | ı           | ı       |         |           | QEIIP<2:0>     |        | 0100 0000 0000 0100       |

| PC1          | 00AA  | I                     | 1      | ı          | 1      | ı      | ı                                 | ı           | ı     | ı      | ı     | ı           | ı       | ı       | I         | 1              | 1      | 0000 0000 0000 0000       |

| Legend       | u= un | u = unimitialized bit | į.     |            |        |        |                                   |             |       |        |       |             |         |         |           |                |        |                           |

Note: Refer to dsPIC30F Family Reference Manual (DS70046) for descriptions of register bit fields.

DS70118E-page 42 Preliminary © 2004 Microchip Technology Inc.

| ABLE 0-1:              |            | NVM REGISTER MAP | בורת<br>ביים בורת | ĀĀ      |        |        |        |       |       |             |       |       |               |                                                                            |         |   |                     |

|------------------------|------------|------------------|-------------------|---------|--------|--------|--------|-------|-------|-------------|-------|-------|---------------|----------------------------------------------------------------------------|---------|---|---------------------|

| File Name Addr. Bit 15 | Addr.      | Bit 15           | Bit 14 Bit 13     | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5 | Bit 4 B       | Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 | 2 Bit 1 | 苗 | All RESETS          |

| NVMCON                 | 0920       | WR               | WRE               | N WRERR | ı      | I      | I      | ı     | - TWR | ı           |       |       | PROC          | PROG0P<6:0>                                                                |         |   | 0000 0000 0000 0000 |

| NVMADR                 | 0762       |                  |                   |         |        |        |        | _     | MMADF | WMADR<15:0> |       |       |               |                                                                            |         |   | mnn mnn nmn nmn     |

| NVMADRU                | 0764       | 1                | 1                 | 1       | ı      | 1      | ı      | ı     | ı     |             |       | Z     | NVMADR<23:16> | 23:16>                                                                     |         |   | mnn mnn 0000 0000   |

| NVMKEY                 | 99/0       | ı                | I                 | 1       | ı      | ı      | J      | ı     | ı     |             |       |       | KEY<7:0>      | <b>6</b>                                                                   |         |   | 0000 0000 0000 0000 |

| ***                    | -1-1-1-1-1 |                  |                   |         |        |        |        |       |       |             |       |       |               |                                                                            |         |   |                     |

Note: Refer to dsPIC30F Family Reference Manual (DS70046) for descriptions of register bit fields.

© 2004 Microchip Technology Inc.

Preliminary

#### 3 Porty

#### 3.1 Hardware

## dsPIC30F2010

#### I/O PORTS 8.0

Note: This data sheet summarizes features of this group Note: Inis data sheet summanuzes reatures or this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the dsPIC30F Family Reference Manual (DS70046).

All of the device pins (except VDD, Vss,  $\overline{\text{MCLR}}$  and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### Parallel I/O (PIO) Ports 8.1

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin

is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins, and writes to the port pins, write the latch (LATx).

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the

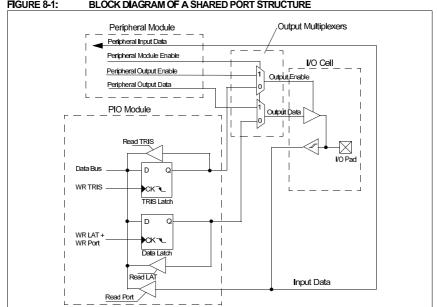

A parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 8-1 shows how ports are shared with other peripherals, and the associated I/O cell (pad) to which they are connected. Table 8-1 shows the formats of the registers for the shared ports, PORTB through PORTG.

BLOCK DIAGRAM OF A SHARED PORT STRUCTURE FIGURE 8-1:

© 2004 Microchip Technology Inc.

**Preliminary**

#### Registry 3.2

# dsPIC30F2010

| _        |            | ashics                | 1010240 | <b>ASPICSUPZUIO PORI REGISTER MAP</b> | 200    | <b>≥</b> | ¥      |       |        |       |       |        |        |        |        |        |        |                     |

|----------|------------|-----------------------|---------|---------------------------------------|--------|----------|--------|-------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| $\vdash$ | me Addr.   | Bit 15                | Bit 14  | Bit 13                                | Bit 12 | 異        | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

| i .      | 9020       | ı                     | I       | I                                     | ı      | ı        | ı      | ı     | ı      | ı     | I     | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1100 0000 0000 |

| 1        | 02C8       | 1                     | ı       | ı                                     | 1      | I        |        | ı     | ı      | I     | ı     | RB5    | RB4    | RB3    | RB2    | RB1    | RBO    | 0000 0000 0000 0000 |

| i .      | 02CB       | ı                     | I       | I                                     | I      | I        | ı      | ı     | ı      | I     | ı     | LATB5  | LATB4  | LATE3  | LATB2  | LATB1  | LATBO  | 0000 0000 0000 0000 |

|          | 02CC       | TRISC15               | TRISC14 | TRISC13                               | -      | ı        | -      | 1     | ı      | ı     | 1     | ı      | ı      | ı      | ı      | ı      | ı      | 1110 0000 0000 0000 |

|          | 02CE       | RC15                  | RC14    | RC13                                  | 1      | I        |        | ı     | ı      | I     | ı     | 1      | ı      | ı      | 1      | ı      | ı      | 0000 0000 0000 0000 |